**Features**

- JEDEC Standard

- $V_{DD} = 1.8V \pm 0.1V$ ,  $V_{DDQ} = 1.8V \pm 0.1V$

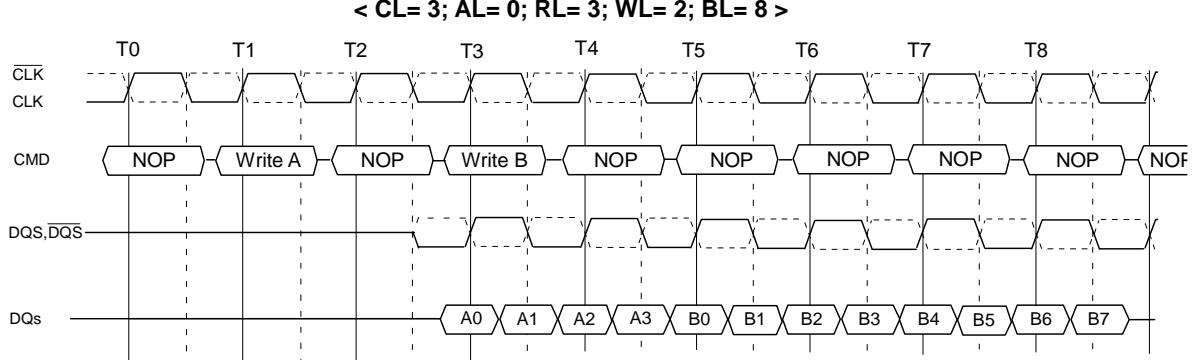

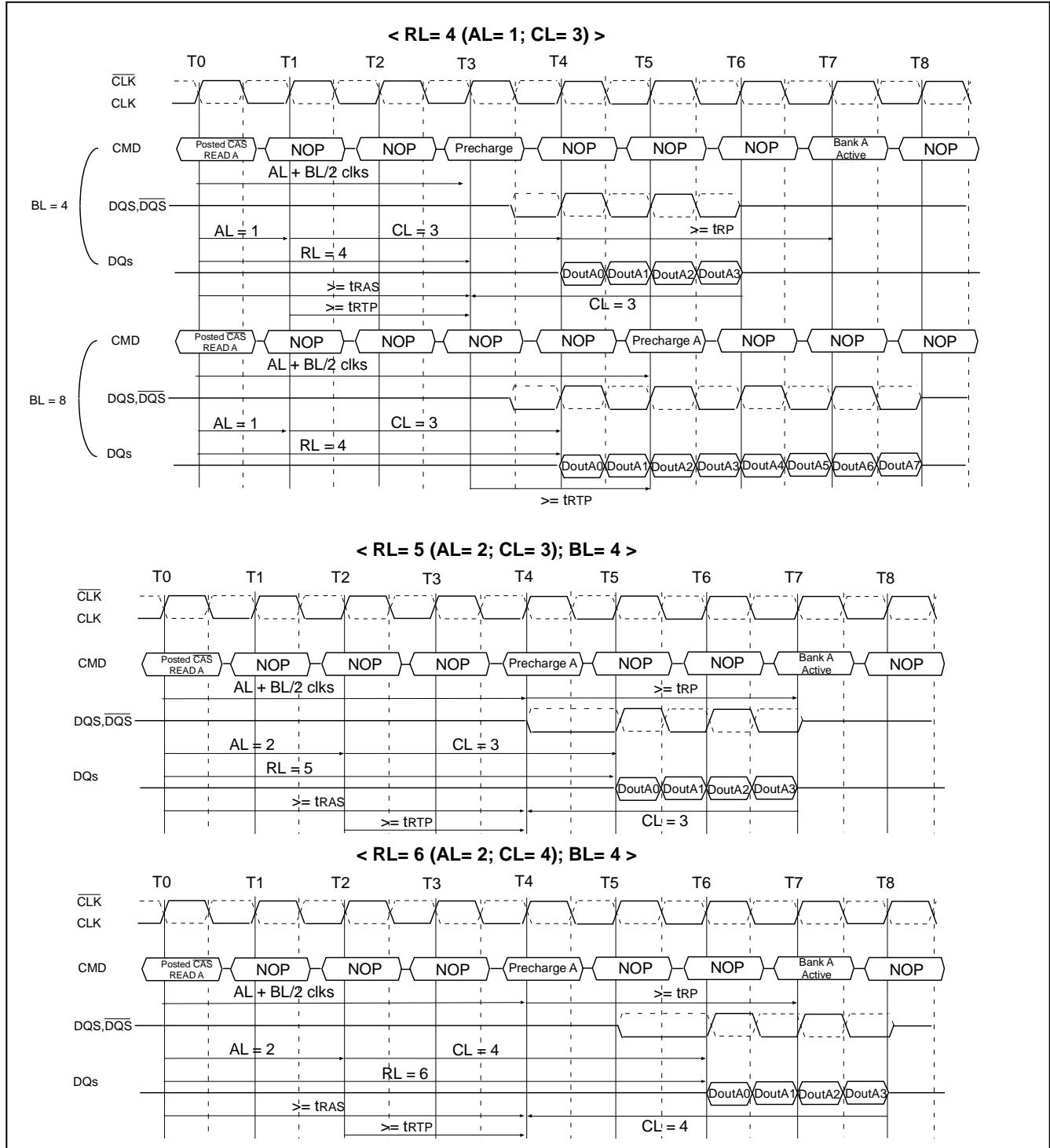

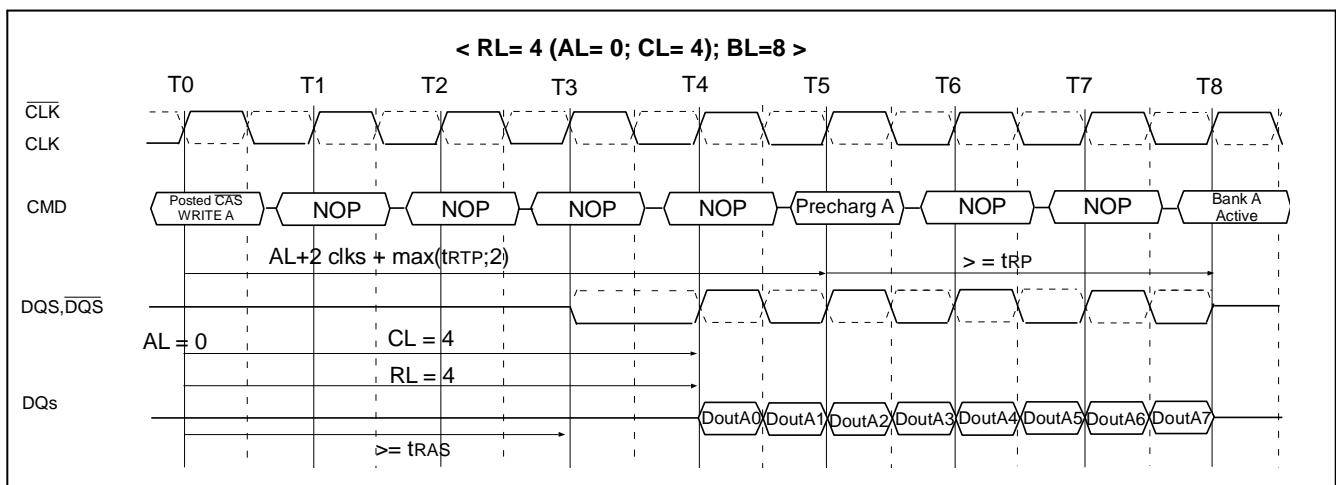

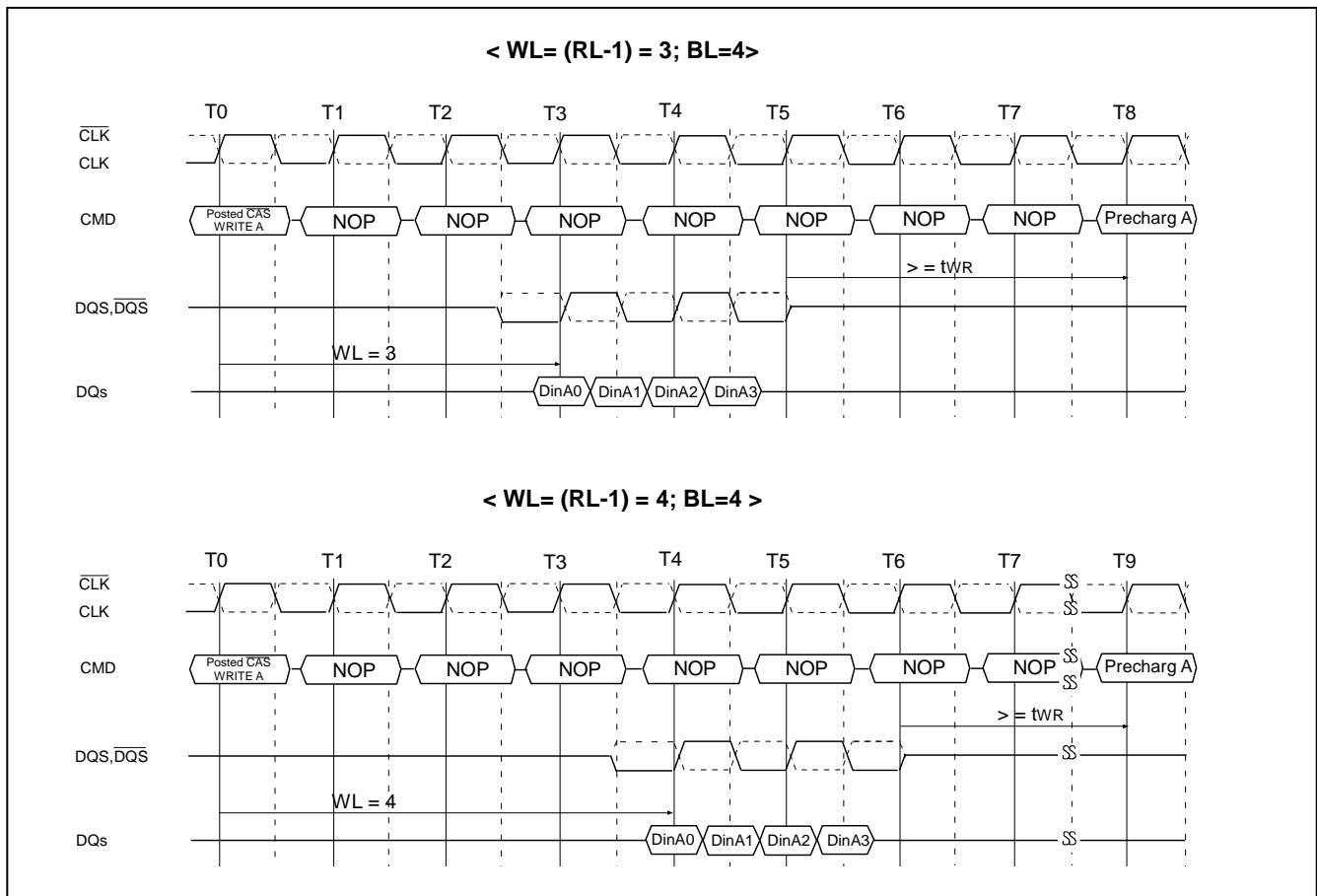

- Internal pipelined double-data-rate architecture; two data access per clock cycle

- Bi-directional differential data strobe (DQS,  $\overline{DQS}$ );  $\overline{DQS}$  can be disabled for single-ended data strobe operation.

- On-chip DLL

- Differential clock inputs (CLK and  $\overline{CLK}$ )

- DLL aligns DQ and DQS transition with CLK transition

- 1KB page size

- Row address: A0 to A11

- Column address: A0 to A8

- Quad bank operation

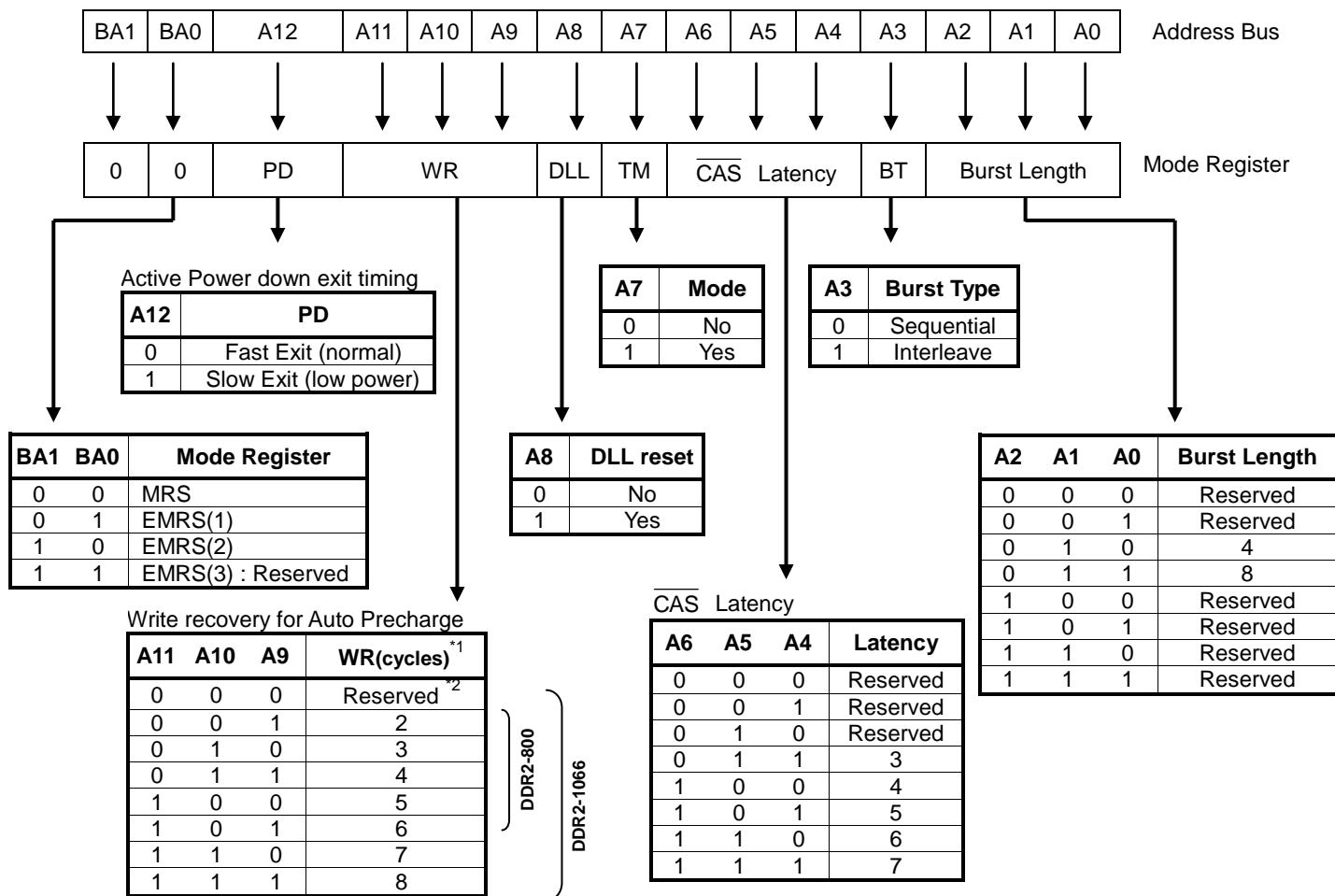

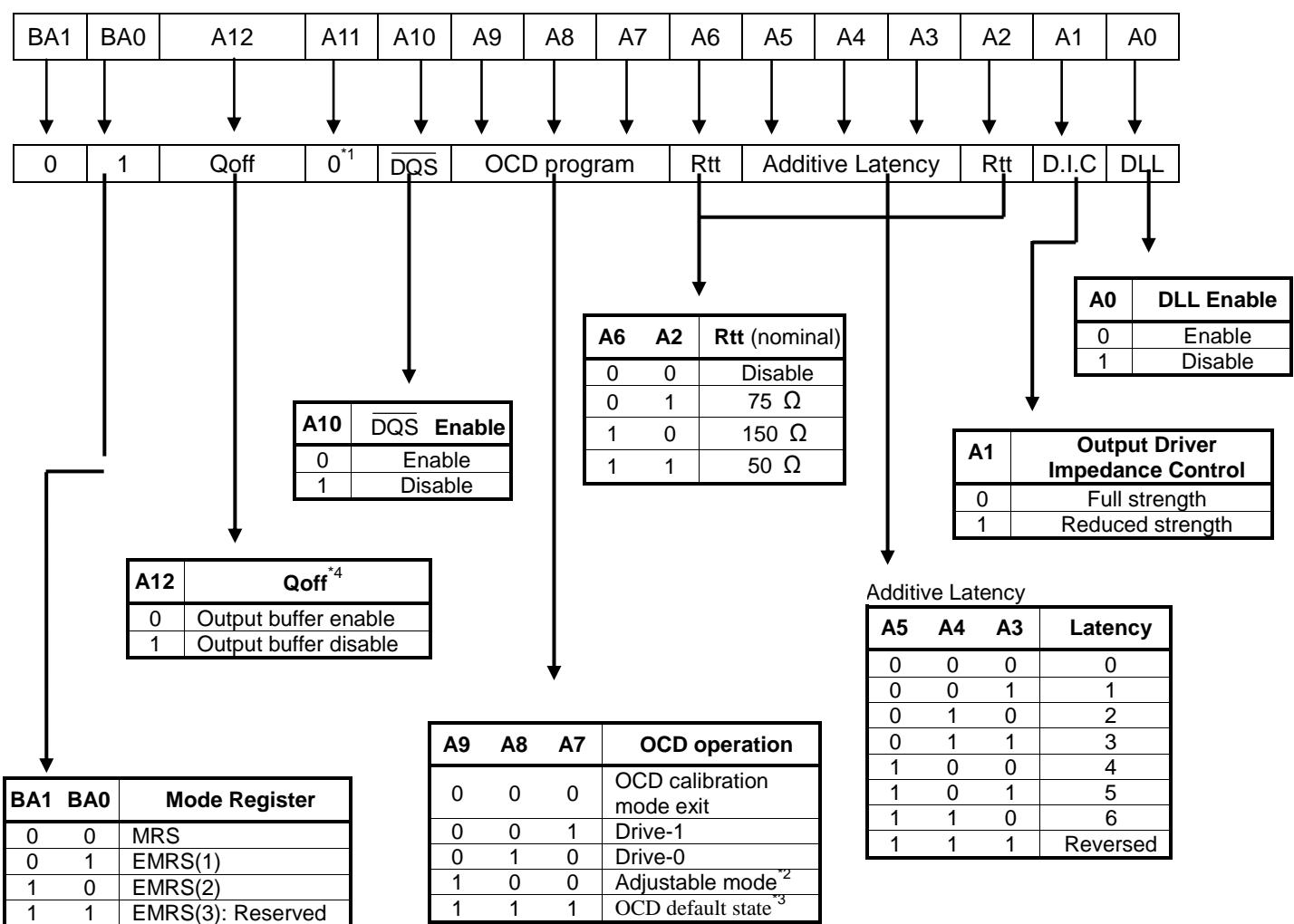

- CAS Latency : 3, 4, 5, 6, 7

- Additive Latency: 0, 1, 2, 3, 4, 5, 6

- Burst Type : Sequential and Interleave

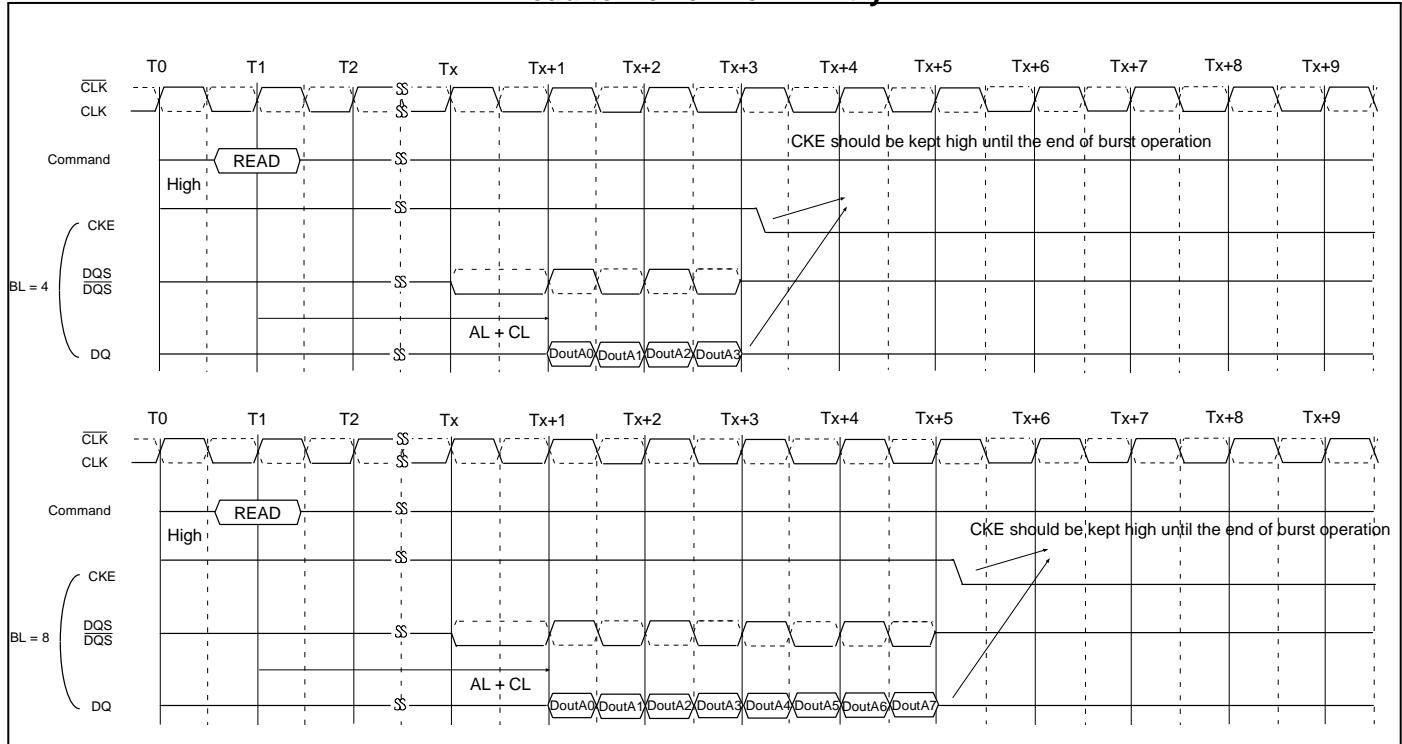

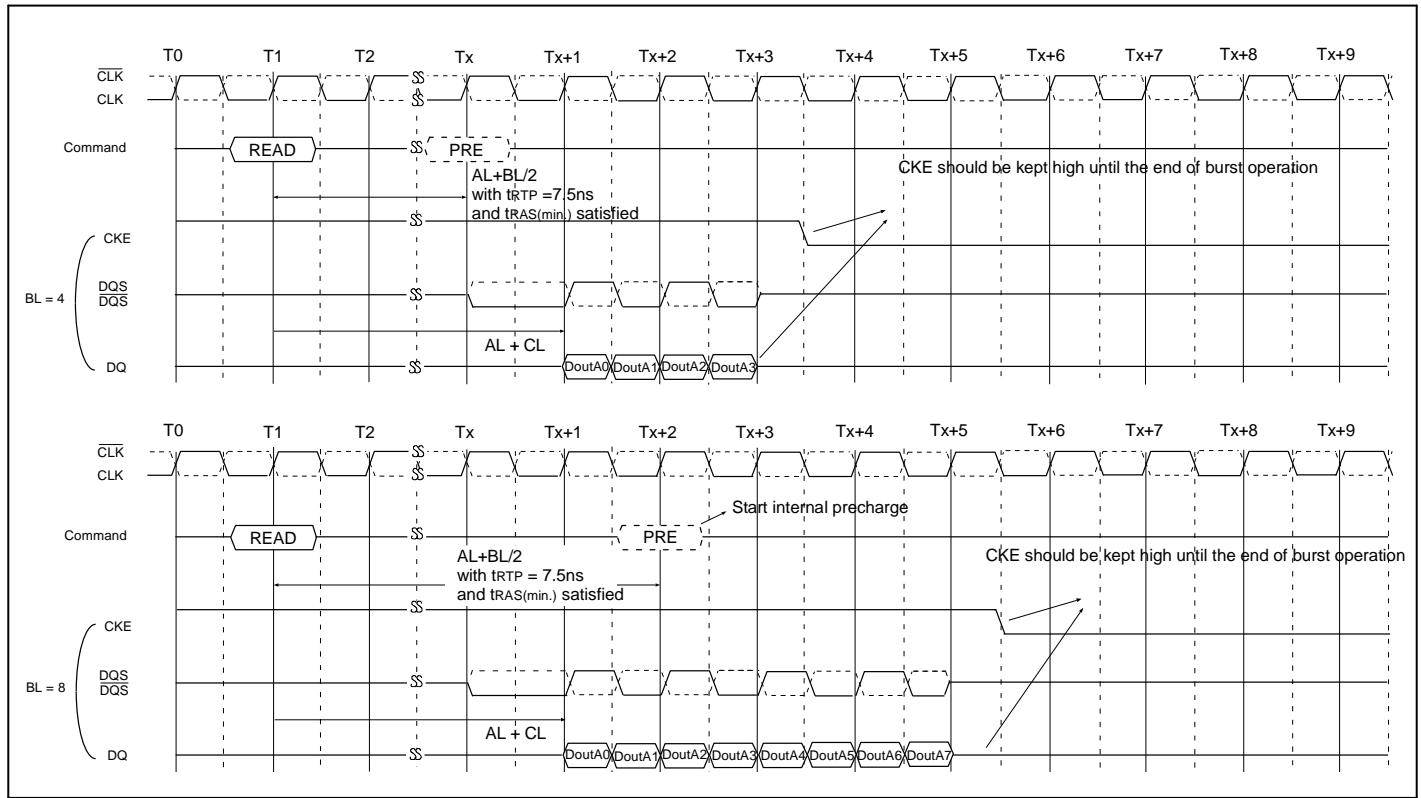

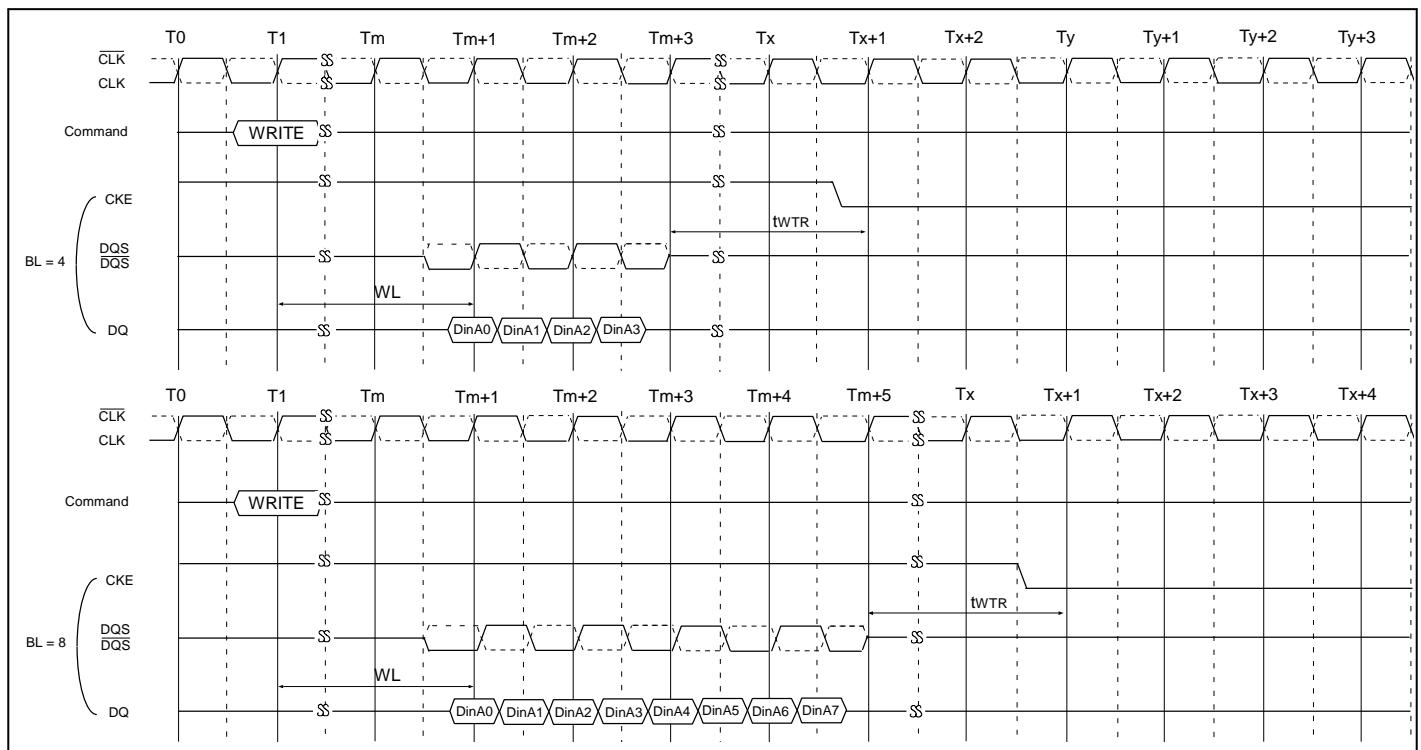

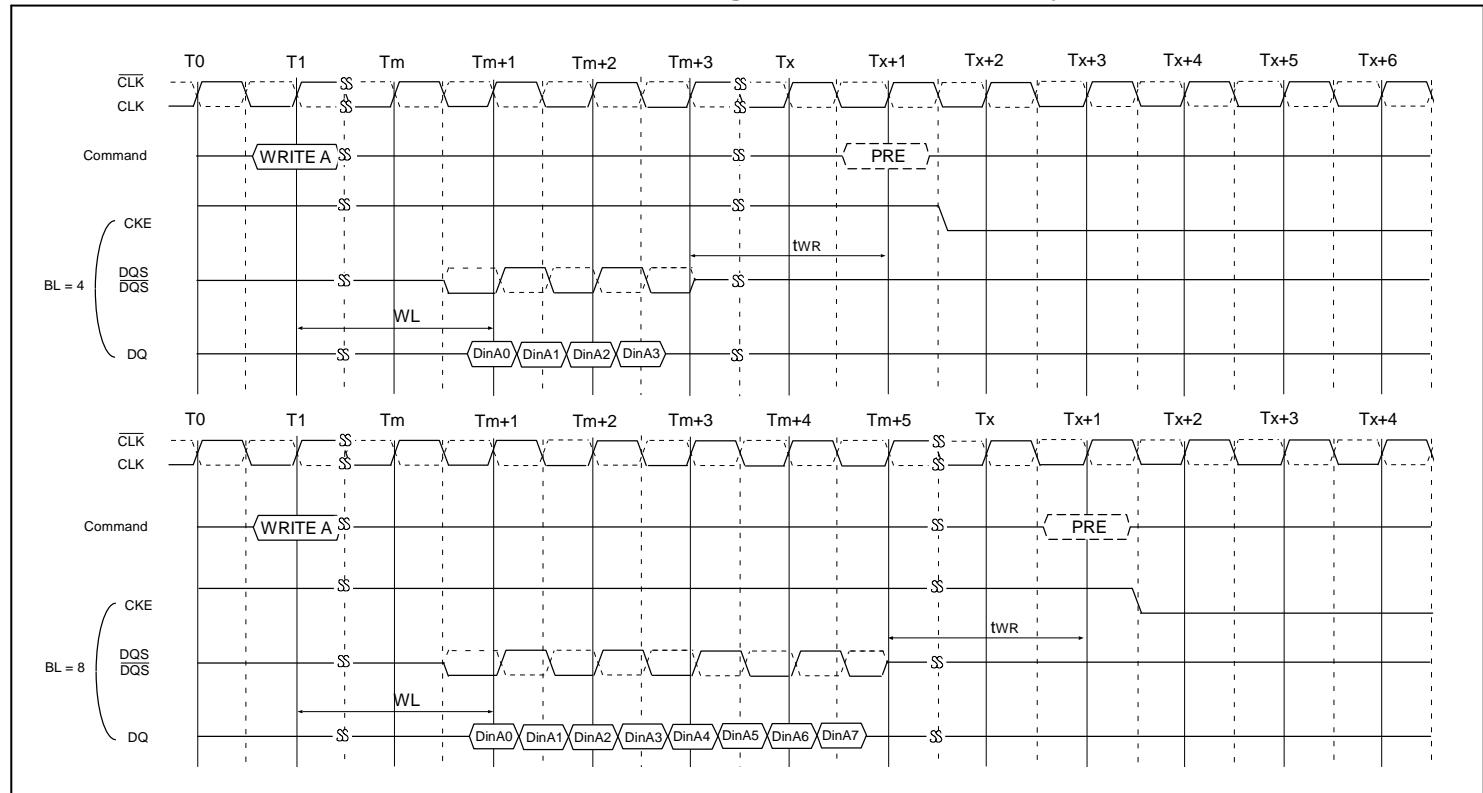

- Burst Length : 4, 8

- All inputs except data & DM are sampled at the rising edge of the system clock(CLK)

- Data I/O transitions on both edges of data strobe (DQS)

- DQS is edge-aligned with data for READ; center-aligned with data for WRITE

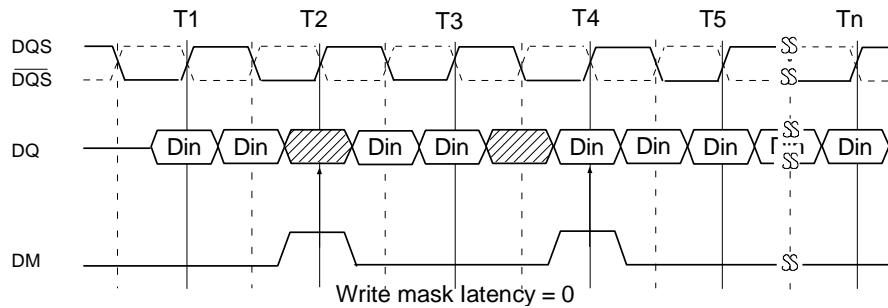

- Data mask (DM) for write masking only

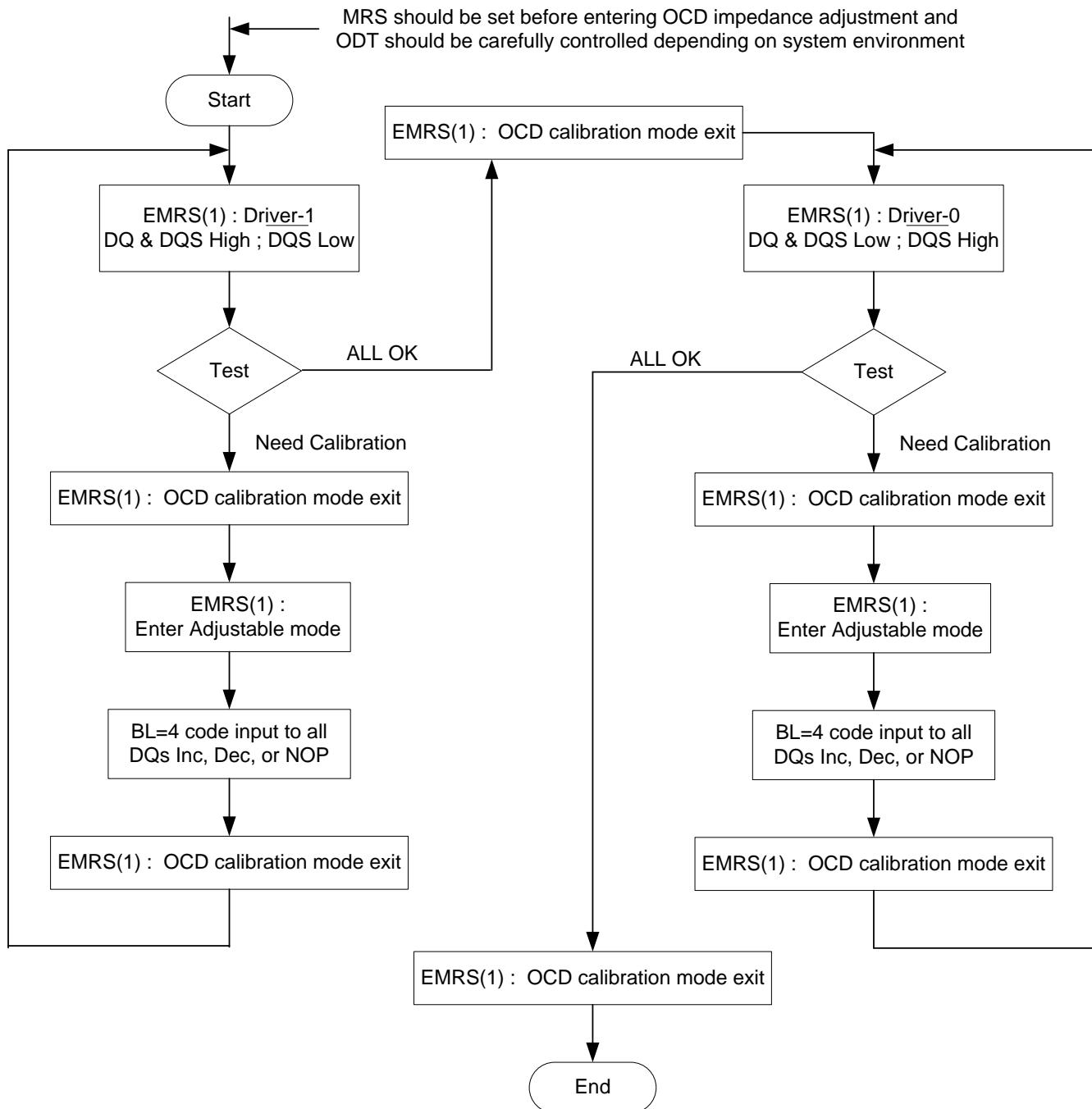

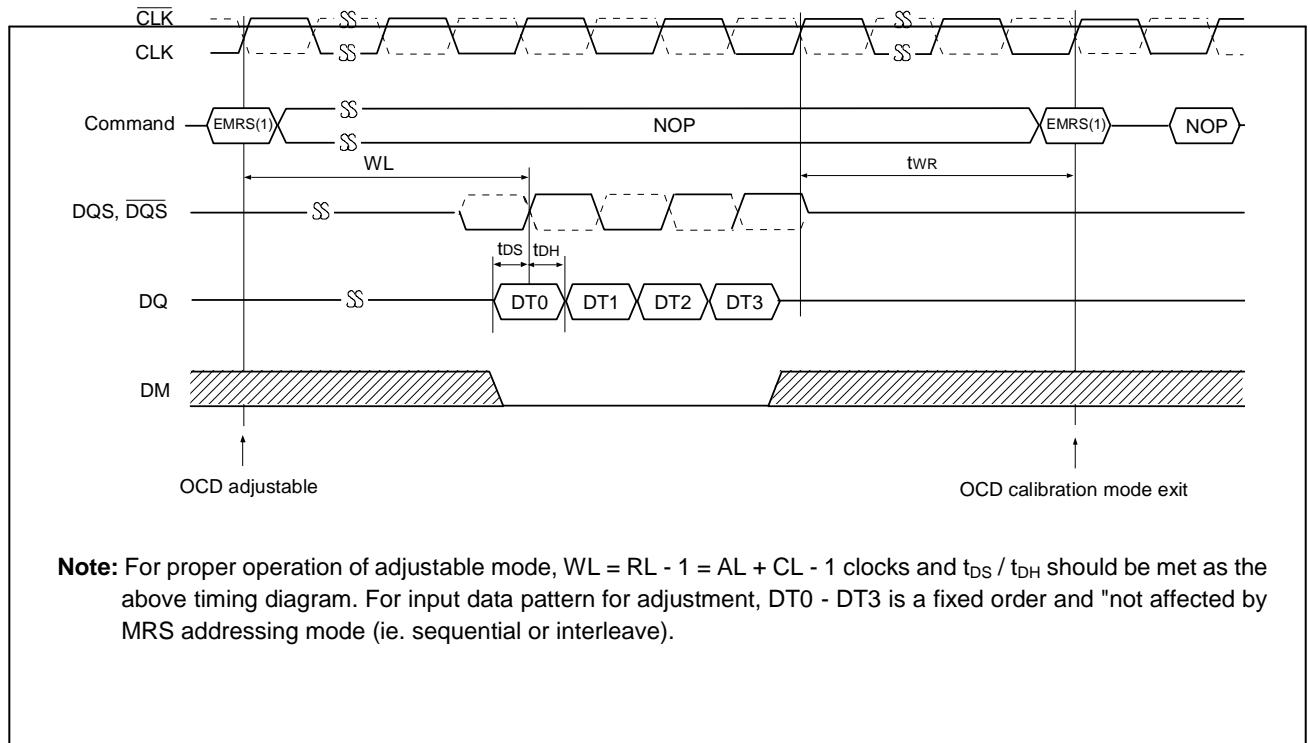

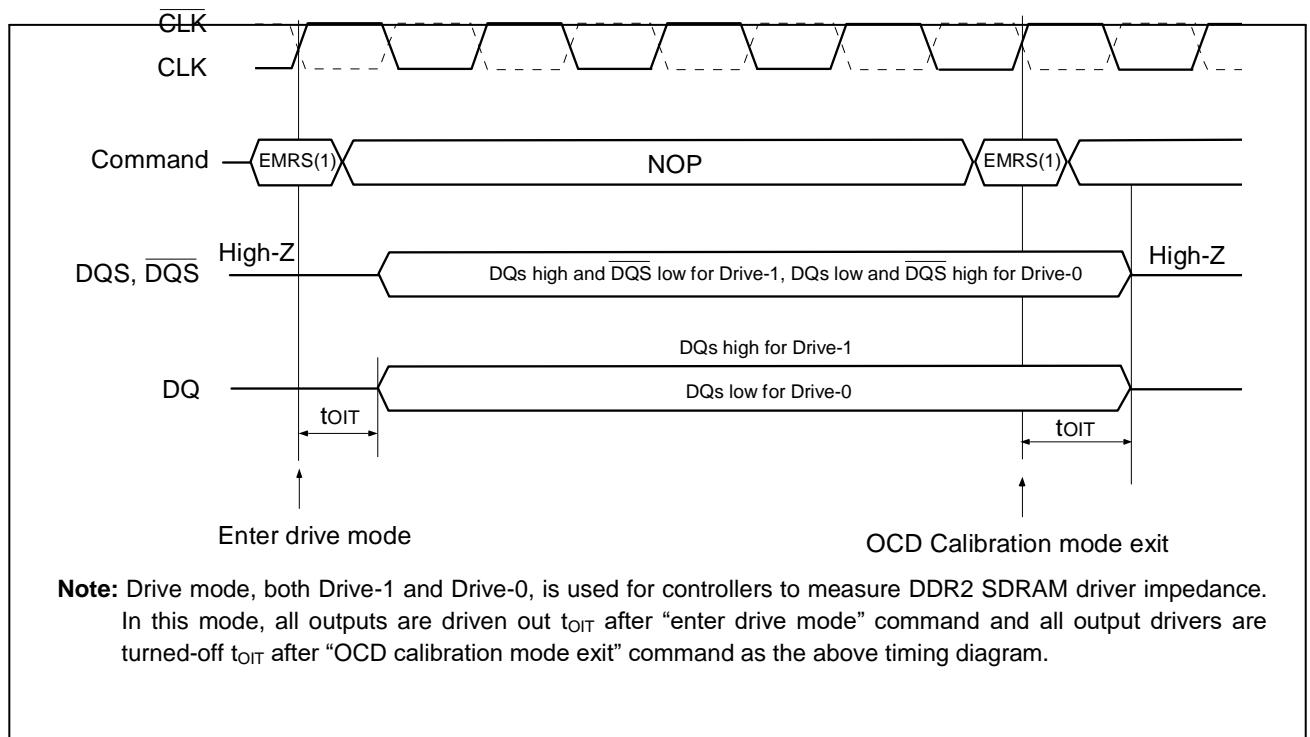

- Off-Chip-Driver (OCD) impedance adjustment

- On-Die-Termination for better signal quality

- Special function support

- 50/ 75/ 150 ohm ODT

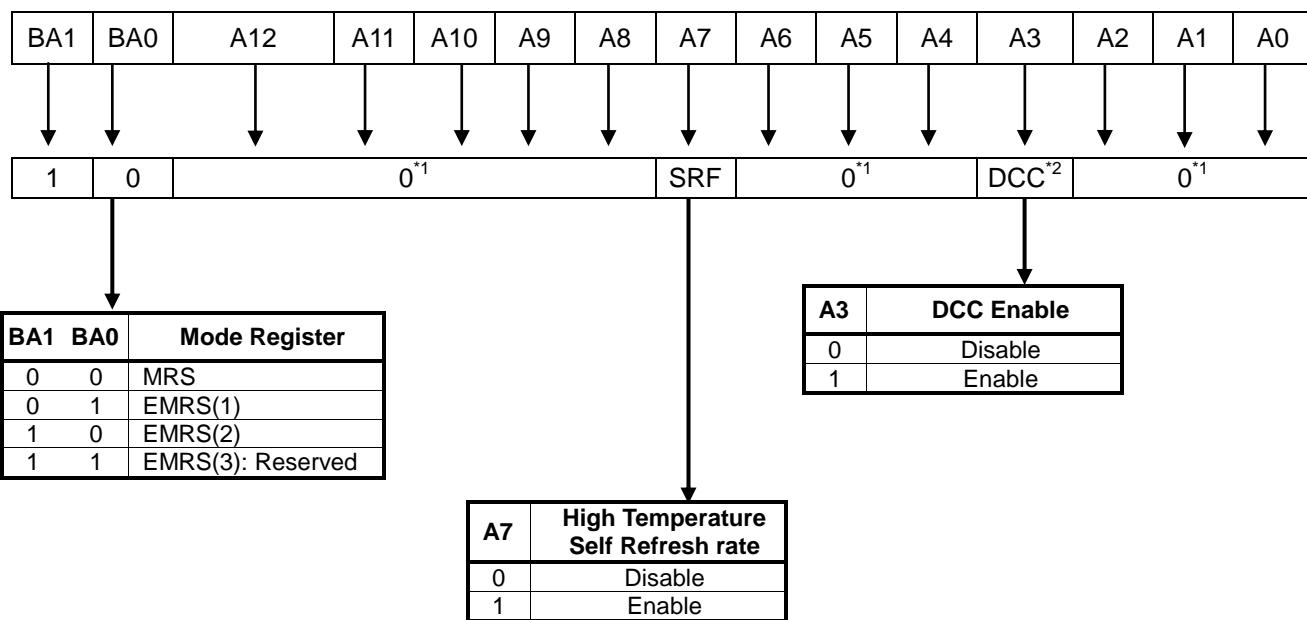

- High Temperature Self refresh rate enable

- DCC (Duty Cycle Corrector)

- Auto & Self refresh

- Refresh cycle :

- 4096 cycles/64ms (15.6 $\mu$ s refresh interval) at  $0^{\circ}\text{C} \leq T_c \leq +85^{\circ}\text{C}$

- 4096 cycles/32ms (7.8 $\mu$ s refresh interval) at  $+85^{\circ}\text{C} < T_c \leq +95^{\circ}\text{C}$

- SSTL\_18 interface

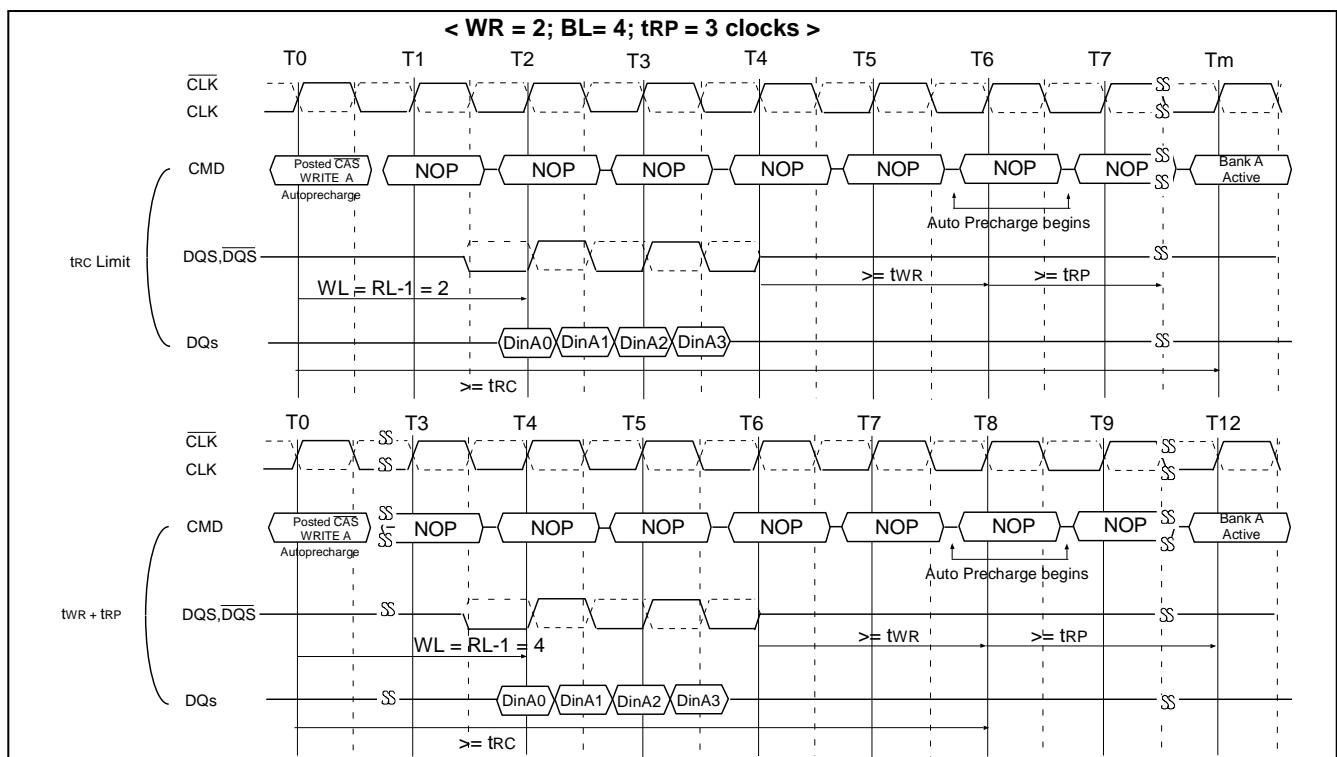

- If  $t_{CK} < 1.875\text{ns}$ , the device can not support Write with Auto Precharge function.

## Ordering Information:

| Product ID                        | Max Freq. | VDD  | Data Rate (CL-tRCD-tRP) | Package                        | Comments |

|-----------------------------------|-----------|------|-------------------------|--------------------------------|----------|

| M14D128168A-1.5BG2Y               | 667MHz    | 1.8V | DDR2-1333 (7-10-10)     | 84 ball BGA<br>A (max) = 1.2mm | Pb-free  |

| M14D128168A-1.6BG2Y <sup>*1</sup> | 600MHz    | 1.8V | DDR2-1200 (7-9-9)       |                                |          |

| M14D128168A-1.8BG2Y               | 533MHz    | 1.8V | DDR2-1066 (7-7-7)       |                                |          |

| M14D128168A-2.5BG2Y               | 400MHz    | 1.8V | DDR2-800 (5-5-5)        |                                |          |

Note: 1. The speed grade is for die only.

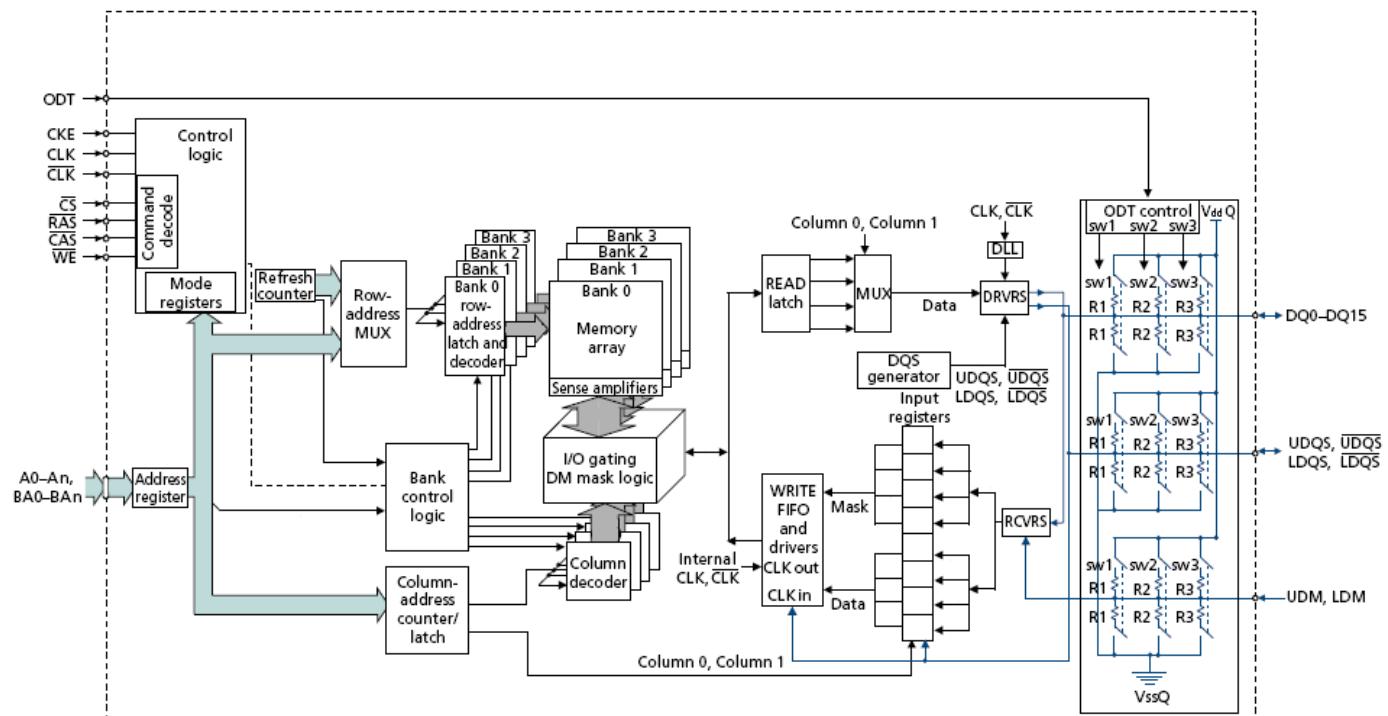

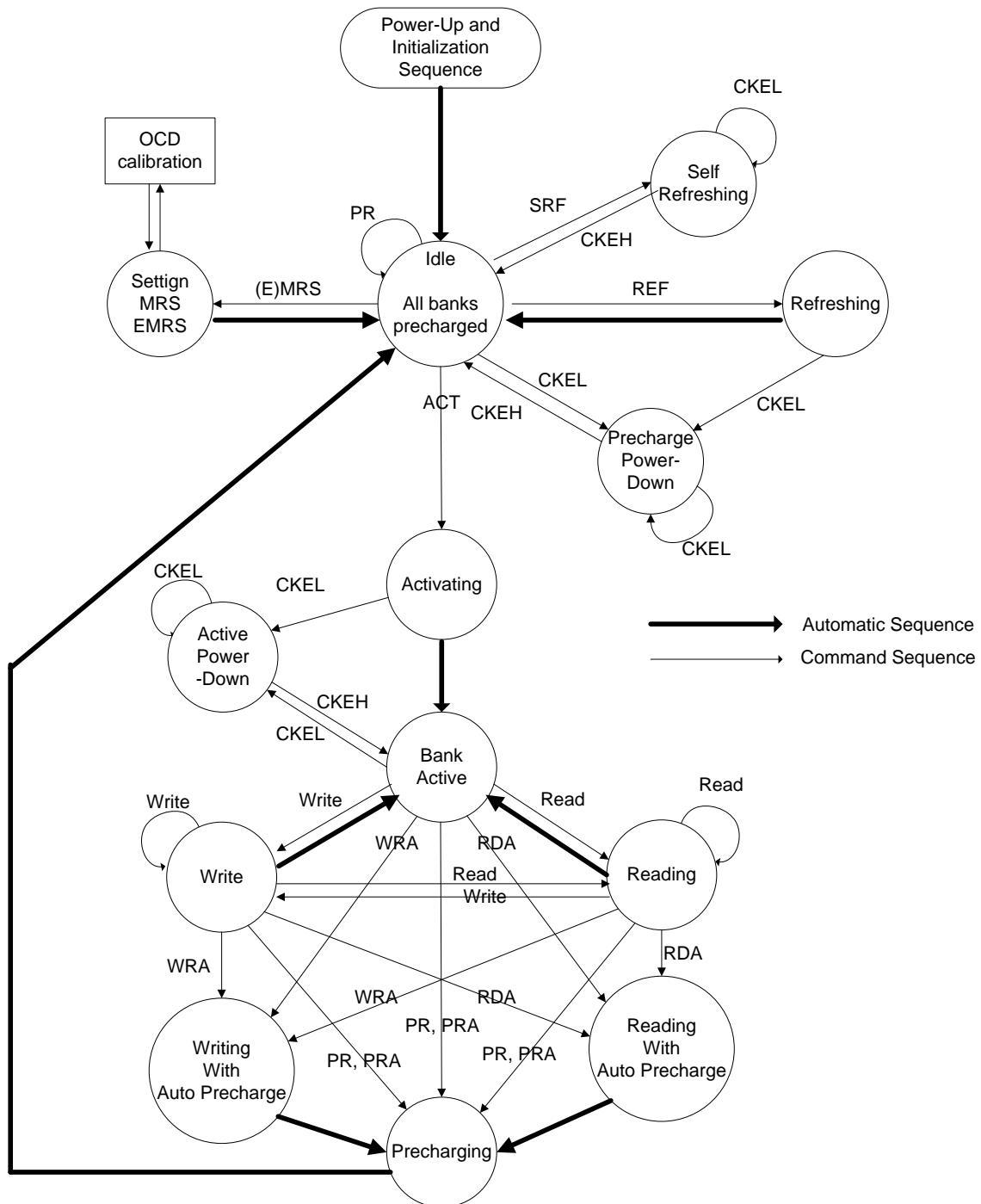

## Functional Block Diagram

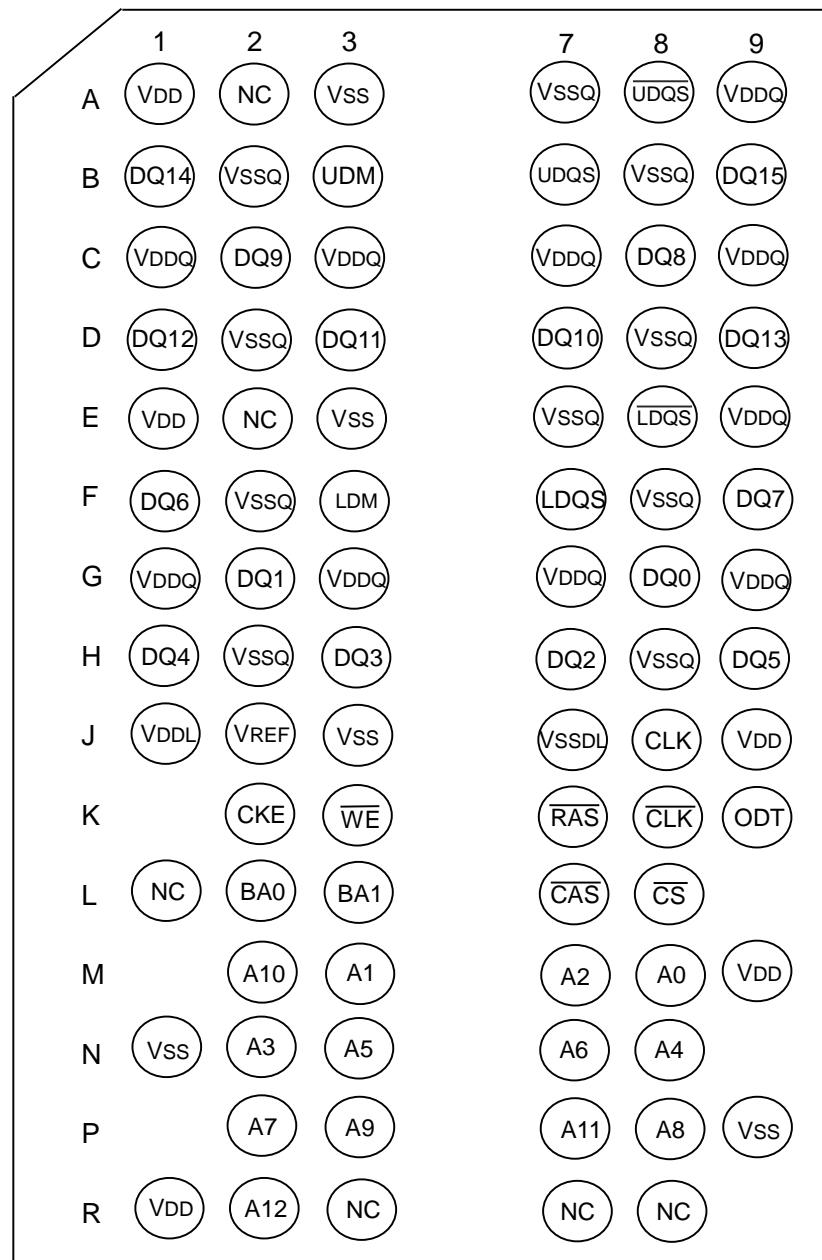

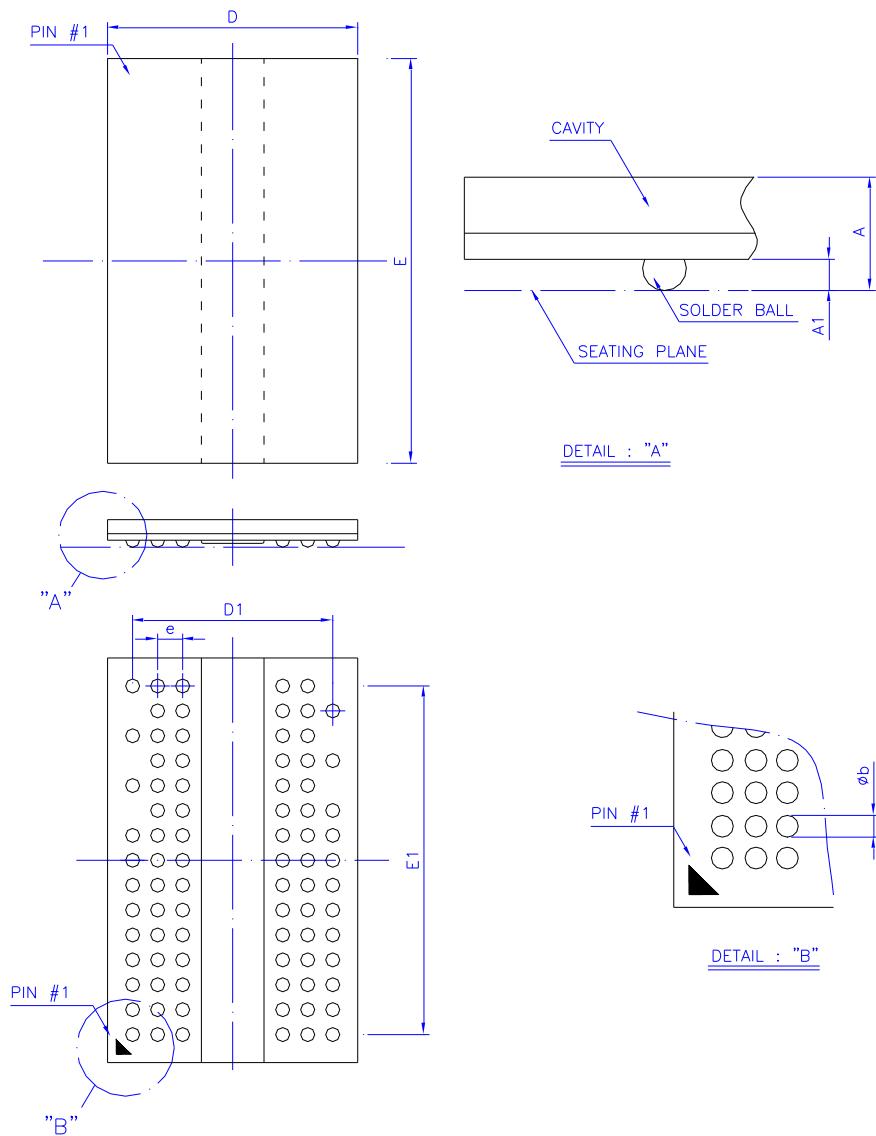

**Ball Configuration (Top View)****(FBGA / VFBGA 84, 8mmX12.5mmX1.2mm Body, 0.8mm Ball Pitch)**

Note: A12 (ball R2) is used for MRS/EMRS.

**Ball Description**

| Pin Name                                                                                            | Function                                                                                                                                                      | Pin Name                     | Function                                                                                        |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------|

| A0~A12,<br>BA0,BA1                                                                                  | Address inputs<br>- Row address A0~A11<br>- Column address A0~A8<br>A12: use for MRS/EMRS<br>A10/AP : Auto Precharge<br>BA0, BA1 : Bank selects (4 Banks)     | DM<br>(LDM, UDM)             | DM is an input mask signal for write data.<br>LDM is DM for DQ0~DQ7 and UDM is DM for DQ8~DQ15. |

| DQ0~DQ15                                                                                            | Data-in/Data-out                                                                                                                                              | CLK, $\overline{\text{CLK}}$ | Differential clock input                                                                        |

| $\overline{\text{RAS}}$                                                                             | Command input                                                                                                                                                 | CKE                          | Clock enable                                                                                    |

| $\overline{\text{CAS}}$                                                                             | Command input                                                                                                                                                 | $\overline{\text{CS}}$       | Chip select                                                                                     |

| $\overline{\text{WE}}$                                                                              | Command input                                                                                                                                                 | $\text{V}_{\text{DDQ}}$      | Supply Voltage for DQ                                                                           |

| $\text{V}_{\text{ss}}$                                                                              | Ground                                                                                                                                                        | $\text{V}_{\text{SSQ}}$      | Ground for DQ                                                                                   |

| $\text{V}_{\text{DD}}$                                                                              | Power                                                                                                                                                         | $\text{V}_{\text{REF}}$      | Reference Voltage                                                                               |

| DQS, $\overline{\text{DQS}}$<br>(LDQS, $\overline{\text{LDQS}}$<br>UDQS, $\overline{\text{UDQS}}$ ) | Bi-directional differential Data Strobe.<br>LDQS and $\overline{\text{LDQS}}$ are DQS for DQ0~DQ7;<br>UDQS and $\overline{\text{UDQS}}$ are DQS for DQ8~DQ15. | $\text{V}_{\text{DDL}}$      | Supply Voltage for DLL                                                                          |

| ODT                                                                                                 | On-Die-Termination.<br>ODT is only applied to DQ0~DQ15, DM, DQS and $\overline{\text{DQS}}$ .                                                                 | $\text{V}_{\text{SSDL}}$     | Ground for DLL                                                                                  |

| NC                                                                                                  | No connection                                                                                                                                                 |                              |                                                                                                 |

**Absolute Maximum Rating**

| Parameter                                                                    | Symbol                                        | Value      | Unit         |

|------------------------------------------------------------------------------|-----------------------------------------------|------------|--------------|

| Voltage on any pin relative to $\text{V}_{\text{ss}}$                        | $\text{V}_{\text{IN}}, \text{V}_{\text{OUT}}$ | -0.5 ~ 2.3 | V            |

| Voltage on $\text{V}_{\text{DD}}$ supply relative to $\text{V}_{\text{ss}}$  | $\text{V}_{\text{DD}}$                        | -1.0 ~ 2.3 | V            |

| Voltage on $\text{V}_{\text{DDL}}$ supply relative to $\text{V}_{\text{ss}}$ | $\text{V}_{\text{DDL}}$                       | -0.5 ~ 2.3 | V            |

| Voltage on $\text{V}_{\text{DDQ}}$ supply relative to $\text{V}_{\text{ss}}$ | $\text{V}_{\text{DDQ}}$                       | -0.5 ~ 2.3 | V            |

| Storage temperature                                                          | $\text{T}_{\text{STG}}$                       | -55 ~ +100 | °C ( Note *) |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Note \*:** Storage Temperature is the case surface temperature on the center/top side of the DRAM.

## Operation Temperature Condition

| Parameter             | Symbol | Value   | Unit |

|-----------------------|--------|---------|------|

| Operation temperature | $T_C$  | 0 ~ +95 | °C   |

Note: 1. Operating temperature is the case surface temperature on the center/top side of the DRAM.

2. Supporting 0 to +85°C with full AC and DC specifications.

Supporting 0 to + 85°C and being able to extend to + 95 °C with doubling auto-refresh commands in frequency to a 32ms period (  $t_{REFI} = 7.9\mu s$  ) and higher temperature Self-Refresh entry via A7 "1" on EMRS(2).

## DC Operation Condition & Specifications

### DC Operation Condition

(Recommended DC operating conditions)

| Parameter                    | Symbol        | Min.                  | Typ.                 | Max.                  | Unit | Note  |

|------------------------------|---------------|-----------------------|----------------------|-----------------------|------|-------|

| Supply voltage               | $V_{DD}$      | 1.7                   | 1.8                  | 1.9                   | V    | 4,7   |

| Supply voltage for DLL       | $V_{DDL}$     | 1.7                   | 1.8                  | 1.9                   | V    | 4,7   |

| Supply voltage for output    | $V_{DDQ}$     | 1.7                   | 1.8                  | 1.9                   | V    | 4,7   |

| Input reference voltage      | $V_{REF}$     | $0.49 \times V_{DDQ}$ | $0.5 \times V_{DDQ}$ | $0.51 \times V_{DDQ}$ | V    | 1,2,7 |

| Termination voltage (system) | $V_{TT}$      | $V_{REF} - 0.04$      | $V_{REF}$            | $V_{REF} + 0.04$      | V    | 3,7   |

| Input logic high voltage     | $V_{IH}$ (DC) | $V_{REF} + 0.125$     | -                    | $V_{DDQ} + 0.3$       | V    |       |

| Input logic low voltage      | $V_{IL}$ (DC) | -0.3                  | -                    | $V_{REF} - 0.125$     | V    |       |

(All voltages referenced to VSS)

| Parameter                                                               | Symbol   | Value | Unit | Note |

|-------------------------------------------------------------------------|----------|-------|------|------|

| Output minimum source DC current ( $V_{DDQ}$ (min); $V_{OUT} = 1.42V$ ) | $I_{OH}$ | -13.4 | mA   | 5,6  |

| Output minimum sink DC current ( $V_{DDQ}$ (min); $V_{OUT} = 0.28V$ )   | $I_{OL}$ | +13.4 | mA   | 5,6  |

#### Note:

1. The value of  $V_{REF}$  may be selected by the user to provide optimum noise margin in the system. Typically the value of  $V_{REF}$  is expected to be about  $0.5 \times V_{DDQ}$  of the transmitting device and  $V_{REF}$  is expected to track variations in  $V_{DDQ}$ .

2. Peak to peak AC noise on  $V_{REF}$  may not exceed  $\pm 2\%$   $V_{REF}$  (DC).

3.  $V_{TT}$  of transmitting device must track  $V_{REF}$  of receiving device.

4.  $V_{DDQ}$  and  $V_{DDL}$  track  $V_{DD}$ . AC parameters are measured with  $V_{DD}$ ,  $V_{DDQ}$  and  $V_{DDL}$  tied together.

5. The DC value of  $V_{REF}$  applied to the receiving device is expected to be set to  $V_{TT}$ .

6.  $T_C = 25^\circ C$ ,  $V_{DD} = V_{DDQ} = 1.8V$ .

7. There is no specific device  $V_{DD}$  supply voltage requirement for SSTL\_18 compliance. However, under all conditions  $V_{DDQ}$  must be less than or equal to  $V_{DD}$ .

**DC Specifications**

(IDD values are for the operation range of Voltage and Temperature)

| Parameter                                     | Symbol | Test Condition                                                                                                                                                                                                                                                                                                                                                               | Version                      |      |      |      | Unit |    |

|-----------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|------|------|------|----|

|                                               |        |                                                                                                                                                                                                                                                                                                                                                                              | -1.5                         | -1.6 | -1.8 | -2.5 |      |    |

| Operating Current (Active - Precharge)        | IDD0   | One bank;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD), t <sub>RC</sub> = t <sub>RC</sub> (IDD), t <sub>RAS</sub> = t <sub>RAS</sub> (IDD)min;<br>CKE is High, CS is HIGH between valid commands;<br>Address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                                                                                        | 100                          | 95   | 85   | 75   | mA   |    |

| Operating Current (Active - Read - Precharge) | IDD1   | One bank; I <sub>OUT</sub> = 0mA;<br>BL = 4, CL = CL(IDD), AL = 0;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD), t <sub>RC</sub> = t <sub>RC</sub> (IDD),<br>t <sub>RAS</sub> = t <sub>RAS</sub> (IDD)min, t <sub>RCD</sub> = t <sub>RCD</sub> (IDD);<br>CKE is HIGH, CS is HIGH between valid commands;<br>Address bus inputs are SWITCHING;<br>Data pattern is same as IDD4W | 130                          | 120  | 100  | 95   | mA   |    |

| Precharge Power-Down Standby Current          | IDD2P  | All banks idle;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD); CKE is LOW;<br>Other control and address bus inputs are STABLE;<br>Data bus inputs are FLOATING                                                                                                                                                                                                                  | 15                           | 15   | 12   | 12   | mA   |    |

| Precharge Quiet Standby Current               | IDD2Q  | All banks idle;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD); CKE is HIGH, CS is HIGH;<br>Other control and address bus inputs are STABLE;<br>Data bus inputs are FLOATING                                                                                                                                                                                                     | 65                           | 65   | 55   | 50   | mA   |    |

| Idle Standby Current                          | IDD2N  | All banks idle;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD); CKE is HIGH, CS is HIGH;<br>Other control and address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                                                                                                                                                                                 | 65                           | 65   | 55   | 50   | mA   |    |

| Active Power-down Standby Current             | IDD3P  | All banks open;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD); CKE is LOW;<br>Other control and address bus inputs are STABLE; Data bus input are FLOATING                                                                                                                                                                                                                      | Fast PDN Exit<br>MRS(12) = 0 | 50   | 50   | 45   | 40   | mA |

|                                               |        |                                                                                                                                                                                                                                                                                                                                                                              | Slow PDN Exit<br>MRS(12) = 1 | 25   | 25   | 18   | 18   |    |

| Active Standby Current                        | IDD3N  | All banks open;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD), t <sub>RAS</sub> = t <sub>RAS</sub> (IDD)max, t <sub>RP</sub> = t <sub>RP</sub> (IDD);<br>CKE is HIGH, CS is HIGH between valid commands;<br>Other control and address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                                                                | 90                           | 90   | 80   | 70   | mA   |    |

| Operation Current (Read)                      | IDD4R  | All banks open, continuous burst Reads, I <sub>OUT</sub> = 0mA;<br>BL = 4, CL = CL (IDD), AL = 0;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD), t <sub>RAS</sub> = t <sub>RAS</sub> (IDD)max, t <sub>RP</sub> = t <sub>RP</sub> (IDD);<br>CKE is HIGH, CS is HIGH between valid commands;<br>Address bus inputs are SWITCHING;<br>Data pattern is the same as IDD4W;           | 250                          | 240  | 210  | 170  | mA   |    |

| Operation Current (Write)                     | IDD4W  | All banks open, continuous burst Writes;<br>BL = 4, CL = CL (IDD), AL = 0;<br>t <sub>CK</sub> = t <sub>CK</sub> (IDD), t <sub>RAS</sub> = t <sub>RAS</sub> (IDD)max, t <sub>RP</sub> = t <sub>RP</sub> (IDD);<br>CKE is HIGH, CS is HIGH between valid commands;<br>Address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                       | 240                          | 230  | 200  | 160  | mA   |    |

| Parameter                                | Symbol | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Version |      |      |      | Unit |

|------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|------|

|                                          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -1.5    | -1.6 | -1.8 | -2.5 |      |

| Burst Refresh Current                    | IDD5   | $t_{CK} = t_{CK}(\text{IDD})$ ;<br>Refresh command every $t_{RFC}(\text{IDD})$ interval;<br>CKE is HIGH, $\overline{CS}$ is HIGH between valid commands;<br>Other control and address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                                                                                                                                                                                                 | 105     | 105  | 100  | 95   | mA   |

| Self Refresh Current                     | IDD6   | Self Refresh Mode;<br>CLK and $\overline{CLK}$ at 0V; $CKE \leq 0.2V$ ;<br>Other control and address bus inputs are FLOATING;<br>Data bus inputs are FLOATING                                                                                                                                                                                                                                                                                                    | 6       | 6    | 6    | 6    | mA   |

| Operating Current<br>(Bank interleaving) | IDD7   | All bank interleaving Reads, $I_{OUT} = 0\text{mA}$ ;<br>$BL = 4$ , $CL = CL(\text{IDD})$ , $AL = t_{RCD}(\text{IDD}) - 1 \times t_{CK}(\text{IDD})$ ;<br>$t_{CK} = t_{CK}(\text{IDD})$ , $t_{RC} = t_{RC}(\text{IDD})$ ,<br>$t_{RRD} = t_{RRD}(\text{IDD})$ , $t_{RCD} = 1 \times t_{CK}(\text{IDD})$ ;<br>CKE is HIGH, $\overline{CS}$ is HIGH between valid commands;<br>Address bus inputs are STABLE during Deslects;<br>Data pattern is the same as IDD4W; | 260     | 250  | 220  | 180  | mA   |

**Note:**

1. IDD specifications are tested after the device is properly initialized.

2. Input slew rate is specified by AC Input Test Condition.

3. IDD parameters are specified with ODT disabled.

4. Data bus consists of DQ, DM, DQS and /DQS, IDD values must be met with all combinations of EMRS bits 10 and 11.

5. Definitions for IDD:

LOW is defined as  $V_{IN} \leq V_{IL}(\text{AC})$  (max.).

HIGH is defined as  $V_{IN} \geq V_{IH}(\text{AC})$  (min.).

STABLE is defined as inputs stable at a HIGH or LOW level.

FLOATING is defined as inputs at  $V_{REF} = V_{DDQ}/2$

SWITCHING is defined as:

Address and control signal Inputs are changed between HIGH and LOW every other clock cycle (once per two clocks), and DQ (not including mask or strobe) signal inputs are changed between HIGH and LOW every other data transfer (once per clock).

6. When  $T_c \geq +85^\circ\text{C}$ , IDD6 must be derated by 80%.

IDD6 will increase by this amount if  $T_c \geq +85^\circ\text{C}$  and double refresh option is still enabled.

7. AC Timing for IDD test conditions

For purposes of IDD testing, the following parameters are to be utilized.

| Parameter                   | -1.5                   | -1.6                 | -1.8                 | -2.5                | Unit            |

|-----------------------------|------------------------|----------------------|----------------------|---------------------|-----------------|

|                             | DDR2-1333<br>(7-10-10) | DDR2-1200<br>(7-9-9) | DDR2-1066<br>(7-7-7) | DDR2-800<br>(5-5-5) |                 |

| CL (IDD)                    | 7                      | 7                    | 7                    | 5                   | t <sub>CK</sub> |

| t <sub>RCD</sub> (IDD)      | 15                     | 15                   | 13.125               | 12.5                | ns              |

| t <sub>RC</sub> (IDD)       | 58.5                   | 58.35                | 58.125               | 57.5                | ns              |

| t <sub>RRD</sub> (IDD)-1KB  | 7.5                    | 8.34                 | 7.5                  | 7.5                 | ns              |

| t <sub>CK</sub> (IDD)       | 1.5                    | 1.667                | 1.875                | 2.5                 | ns              |

| t <sub>RAS</sub> (IDD) min. | 45                     | 45                   | 40                   | 45                  | ns              |

| t <sub>RAS</sub> (IDD) max. | 70000                  |                      |                      |                     | ns              |

| t <sub>RP</sub> (IDD)       | 15                     | 15                   | 13.125               | 12.5                | ns              |

| t <sub>RFC</sub> (IDD)      | 90                     | 90                   | 75                   | 75                  | ns              |

## AC Operation Conditions &amp; Timing Specification

## AC Operation Conditions

| Parameter                     | Symbol       | -1.5/1.6/1.8                 |                              | -2.5                         |                              | Unit | Note |

|-------------------------------|--------------|------------------------------|------------------------------|------------------------------|------------------------------|------|------|

|                               |              | Min.                         | Max.                         | Min.                         | Max.                         |      |      |

| Input High (Logic 1) Voltage  | $V_{IH}(AC)$ | $V_{REF} + 0.2$              |                              | $V_{REF} + 0.2$              |                              | V    |      |

| Input Low (Logic 0) Voltage   | $V_{IL}(AC)$ |                              | $V_{REF} - 0.2$              |                              | $V_{REF} - 0.2$              | V    |      |

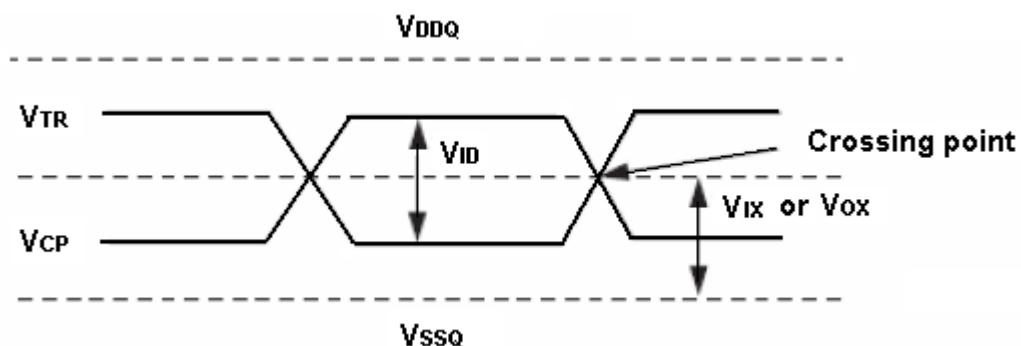

| Input Differential Voltage    | $V_{ID}(AC)$ | 0.5                          | $V_{DDQ} + 0.6$              | 0.5                          | $V_{DDQ}$                    | V    | 1    |

| Input Crossing Point Voltage  | $V_{IX}(AC)$ | $0.5 \times V_{DDQ} - 0.175$ | $0.5 \times V_{DDQ} + 0.175$ | $0.5 \times V_{DDQ} - 0.175$ | $0.5 \times V_{DDQ} + 0.175$ | V    | 2    |

| Output Crossing Point Voltage | $V_{Ox}(AC)$ | $0.5 \times V_{DDQ} - 0.125$ | $0.5 \times V_{DDQ} + 0.125$ | $0.5 \times V_{DDQ} - 0.125$ | $0.5 \times V_{DDQ} + 0.125$ | V    | 2    |

## Note:

- $V_{ID}(AC)$  specifies the input differential voltage  $|V_{TR} - V_{CP}|$  required for switching, where  $V_{TR}$  is the true input signal (such as CLK, DQS) and  $V_{CP}$  is the complementary input signal (such as  $\overline{CLK}$ ,  $\overline{DQS}$ ). The minimum value is equal to  $V_{IH}(AC) - V_{IL}(AC)$ .

- The typical value of  $V_{IX}$  /  $V_{Ox}(AC)$  is expected to be about  $0.5 \times V_{DDQ}$  of the transmitting device and  $V_{IX}$  /  $V_{Ox}(AC)$  is expected to track variations in  $V_{DDQ}$ .  $V_{IX}$  /  $V_{Ox}(AC)$  indicates the voltage at which differential input / output signals must cross.

## Input / Output Capacitance

| Parameter                                                                                                                  | Symbol    | Min. | Max. | Unit | Note |

|----------------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|------|

| Input capacitance<br>(A0~A12, BA0~BA1, CKE, $\overline{CS}$ , $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ , ODT) | $C_{IN1}$ | 2    | 5    | pF   | 1    |

| Input capacitance (CLK, $\overline{CLK}$ )                                                                                 | $C_{IN2}$ | 2    | 5    | pF   | 1    |

| DQS, $\overline{DQS}$ & Data input/output capacitance                                                                      | $C_{I/O}$ | 2    | 5    | pF   | 2    |

| Input capacitance (DM)                                                                                                     | $C_{IN3}$ | 2    | 5    | pF   | 2    |

Note: 1. Maximum capacitance delta is 0.25 pF.

2. Maximum capacitance delta is 0.5 pF.

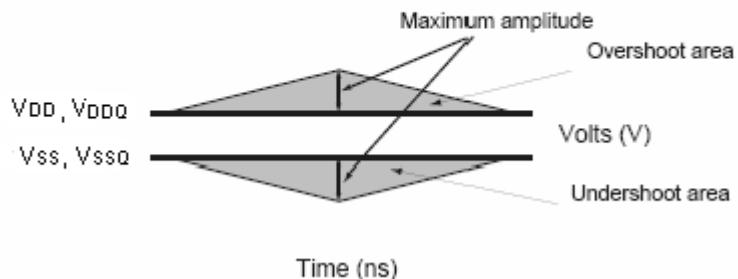

## AC Overshoot / Undershoot Specification

| Parameter                                     | Pin                                                                                                                                   | Value        |      | Unit |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|

|                                               |                                                                                                                                       | -1.5/1.6/1.8 | -2.5 |      |

| Maximum peak amplitude allowed for overshoot  | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.5          |      | V    |

| Maximum peak amplitude allowed for undershoot | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.5          |      | V    |

| Maximum overshoot area above $V_{DD}$         | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.5          | 0.66 | V-ns |

|                                               | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.19         | 0.23 | V-ns |

| Maximum undershoot area below $V_{SS}$        | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.5          | 0.66 | V-ns |

|                                               | Address, CKE, $\overline{CS}$ , RAS, $\overline{CAS}$ , $\overline{WE}$ , ODT, CLK, $\overline{CLK}$ , DQ, DQS, $\overline{DQS}$ , DM | 0.19         | 0.23 | V-ns |

Overshoot/Ubershoot Definition

## AC Operating Test Conditions

| Parameter                                               | Value                | Unit | Note |

|---------------------------------------------------------|----------------------|------|------|

| Input reference voltage ( $V_{REF}$ )                   | $0.5 \times V_{DDQ}$ | V    | 1    |

| Input signal maximum peak swing ( $V_{SWING(max.)}$ )   | 1.0                  | V    | 1    |

| Input signal minimum slew rate (SLEW)                   | 1.0                  | V/ns | 2,3  |

| Input level                                             | $V_{IH} / V_{IL}$    | V    |      |

| Input timing measurement reference level                | $V_{REF}$            | V    |      |

| Output timing measurement reference level ( $V_{OTR}$ ) | $0.5 \times V_{DDQ}$ | V    | 4    |

## Note:

1. Input waveform timing is referenced to the input signal crossing through the  $V_{IH} / V_{IL}$  (AC) level applied to the device under test.

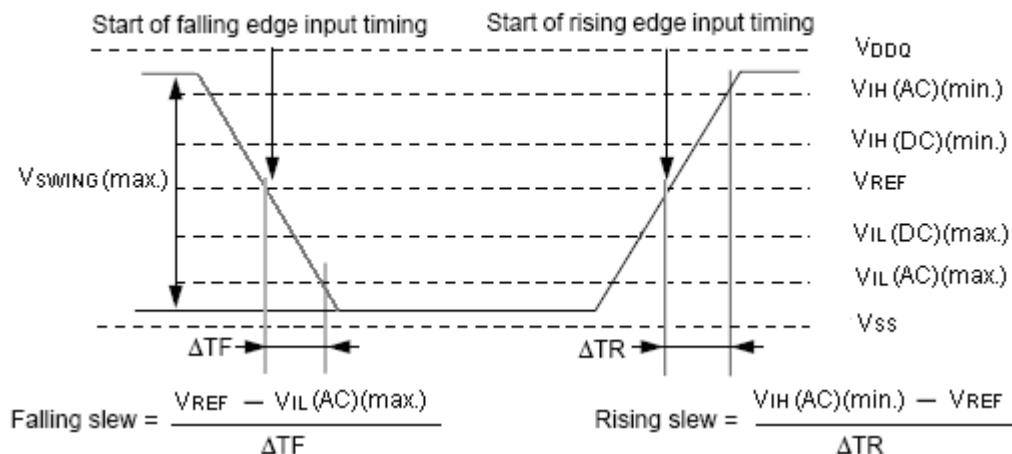

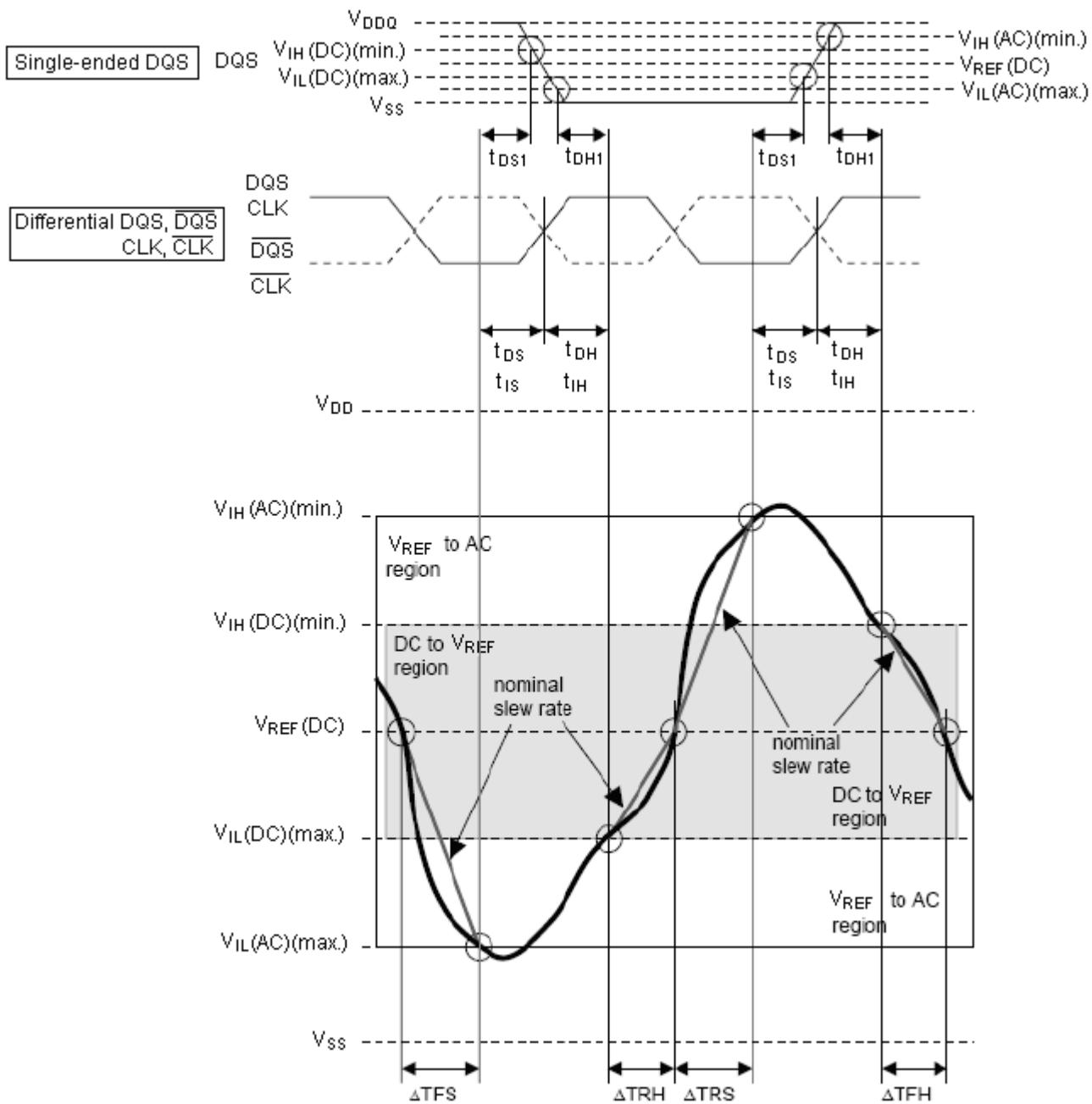

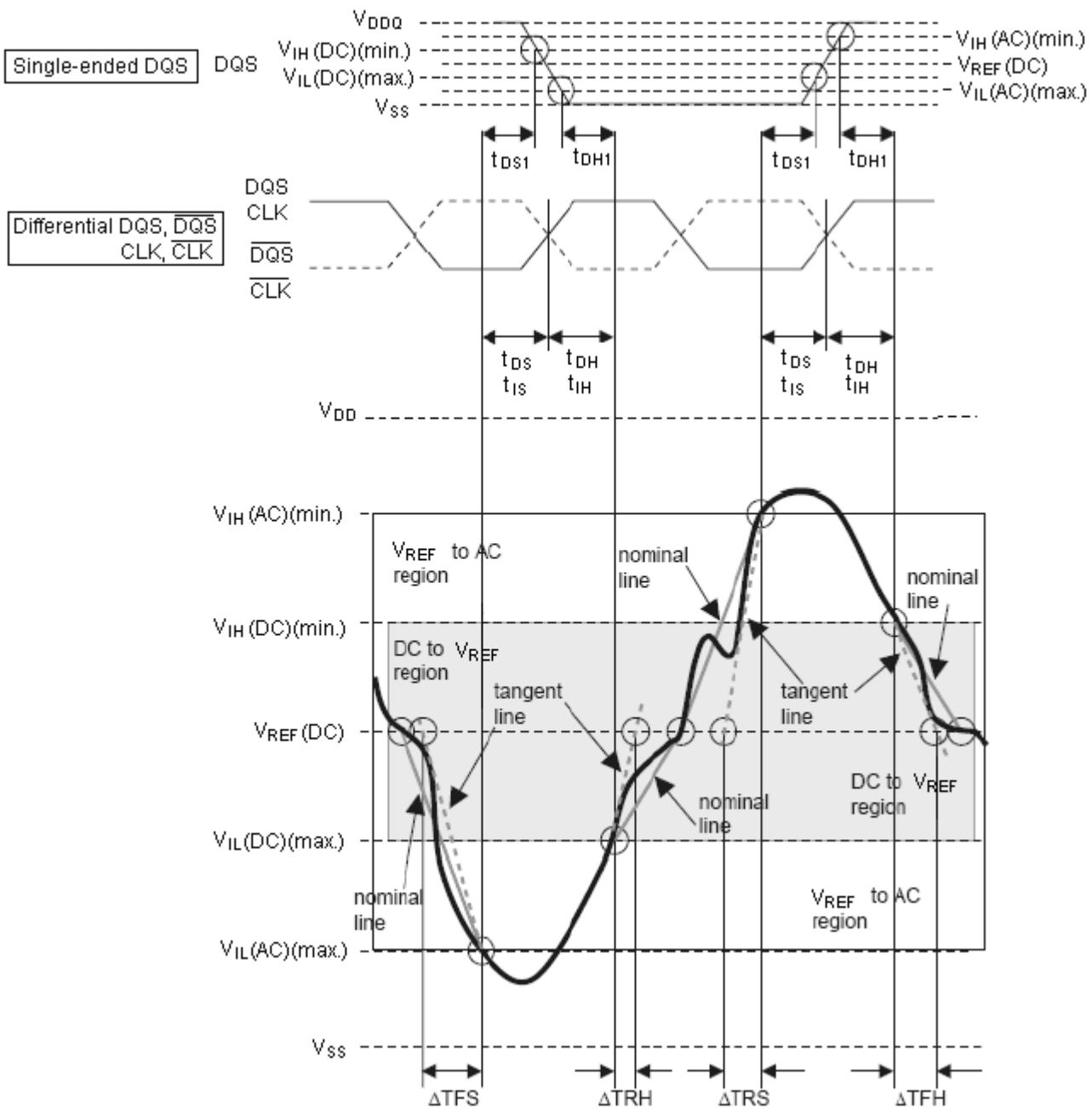

2. The input signal minimum slew rate is to be maintained over the range from  $V_{REF}$  to  $V_{IH}$  (AC) (min.) for rising edges and the range from  $V_{REF}$  to  $V_{IL}$  (AC)(max.) for falling edges as shown in the below figure.

3. AC timings are referenced with input waveforms switching from  $V_{IL}$  (AC) to  $V_{IH}$  (AC) on the positive transitions and  $V_{IH}$  (AC) to  $V_{IL}$  (AC) on the negative transitions.

4. The  $V_{DDQ}$  of the device under test is reference.

## AC Input Test Signal Wave forms

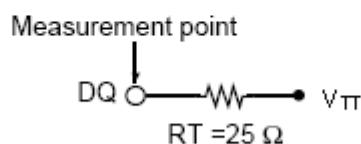

## Output Load

## AC Timing Parameter &amp; Specifications

| Parameter                                                 |      | Symbol          | -1.5                                                |                 | -1.6                                                |                 | Unit           | Note |

|-----------------------------------------------------------|------|-----------------|-----------------------------------------------------|-----------------|-----------------------------------------------------|-----------------|----------------|------|

|                                                           |      |                 | Min.                                                | Max.            | Min.                                                | Max.            |                |      |

| Clock period                                              | CL=7 | $t_{CK}$ (avg)  | 1500                                                | 3000            | 1667                                                | 3000            | ps             | 13   |

| DQ output access time from CLK/ $\overline{CLK}$          |      | $t_{AC}$        | -350                                                | +350            | -350                                                | +350            | ps             | 10   |

| CLK high-level width                                      |      | $t_{CH}$ (avg)  | 0.48                                                | 0.52            | 0.48                                                | 0.52            | $t_{CK}$ (avg) | 13   |

| CLK low-level width                                       |      | $t_{CL}$ (avg)  | 0.48                                                | 0.52            | 0.48                                                | 0.52            | $t_{CK}$ (avg) | 13   |

| DQS output access time from CLK/ $\overline{CLK}$         |      | $t_{DQCK}$      | -300                                                | +300            | -300                                                | +300            | ps             | 10   |

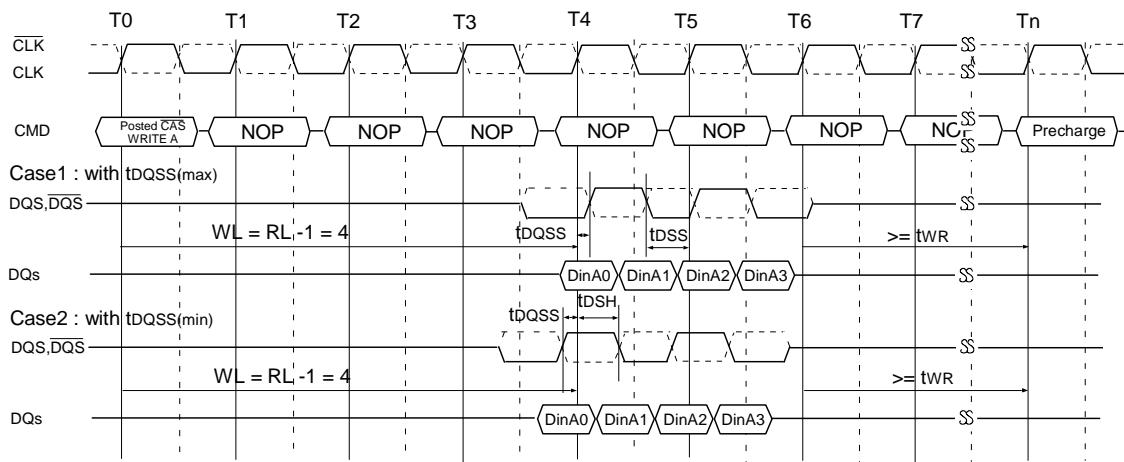

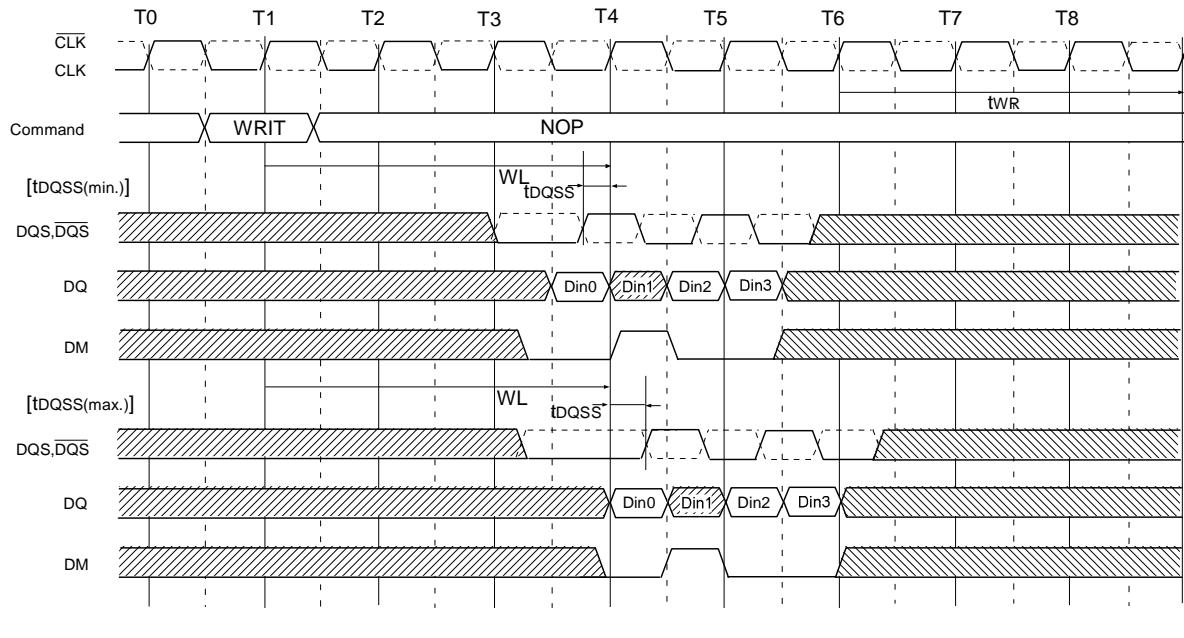

| Clock to first rising edge of DQS delay                   |      | $t_{DQSS}$      | -0.25                                               | +0.25           | -0.25                                               | +0.25           | $t_{CK}$ (avg) |      |

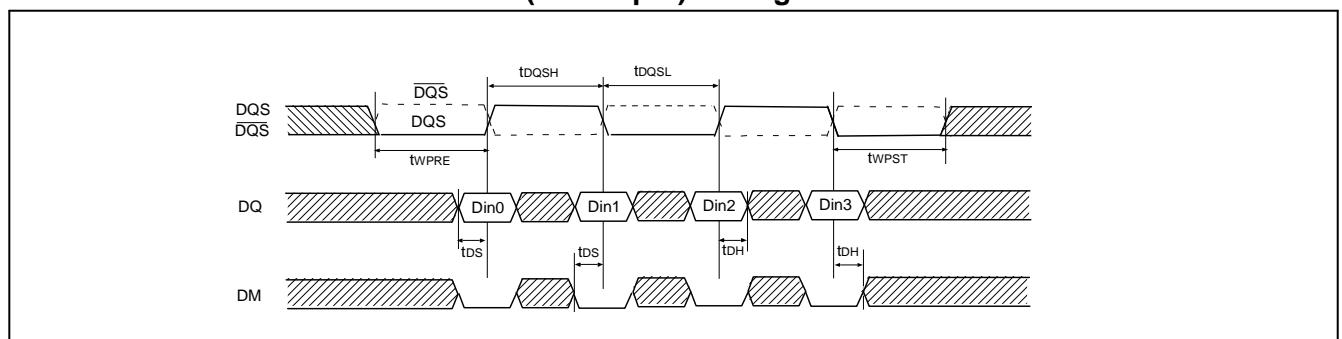

| Data-in and DM setup time (to DQS)                        |      | $t_{DS}$ (base) | 200                                                 |                 | 200                                                 |                 | ps             | 4    |

| Data-in and DM hold time (to DQS)                         |      | $t_{DH}$ (base) | 200                                                 |                 | 200                                                 |                 | ps             | 5    |

| DQ and DM input pulse width (for each input)              |      | $t_{DIPW}$      | 0.35                                                |                 | 0.35                                                |                 | $t_{CK}$ (avg) |      |

| Address and Control Input setup time                      |      | $t_{IS}$ (base) | 125                                                 |                 | 125                                                 |                 | ps             | 4    |

| Address and Control Input hold time                       |      | $t_{IH}$ (base) | 200                                                 |                 | 200                                                 |                 | ps             | 5    |

| Control and Address input pulse width                     |      | $t_{IPW}$       | 0.6                                                 |                 | 0.6                                                 |                 | $t_{CK}$ (avg) |      |

| DQS input high pulse width                                |      | $t_{DQSH}$      | 0.44                                                |                 | 0.44                                                |                 | $t_{CK}$ (avg) |      |

| DQS input low pulse width                                 |      | $t_{DQSL}$      | 0.44                                                |                 | 0.44                                                |                 | $t_{CK}$ (avg) |      |

| DQS falling edge to CLK rising setup time                 |      | $t_{DSS}$       | 0.2                                                 |                 | 0.2                                                 |                 | $t_{CK}$ (avg) |      |

| DQS falling edge from CLK rising hold time                |      | $t_{DSH}$       | 0.2                                                 |                 | 0.2                                                 |                 | $t_{CK}$ (avg) |      |

| Data strobe edge to output data edge                      |      | $t_{DQSQ}$      |                                                     | 250             |                                                     | 250             | ps             |      |

| Data-out high-impedance window from CLK/ $\overline{CLK}$ |      | $t_{HZ}$        |                                                     | $t_{AC}(\max.)$ |                                                     | $t_{AC}(\max.)$ | ps             | 10   |

| Data-out low-impedance window from CLK/ $\overline{CLK}$  |      | $t_{LZ}$ (DQS)  | $t_{AC}(\min.)$                                     | $t_{AC}(\max.)$ | $t_{AC}(\min.)$                                     | $t_{AC}(\max.)$ | ps             | 10   |

| DQ low-impedance window from CLK/ $\overline{CLK}$        |      | $t_{LZ}$ (DQ)   | $2 \times t_{AC}(\min.)$                            | $t_{AC}(\max.)$ | $2 \times t_{AC}(\min.)$                            | $t_{AC}(\max.)$ | ps             | 10   |

| Half clock period                                         |      | $t_{HP}$        | Min<br>( $t_{CL}(\text{abs}), t_{CH}(\text{abs})$ ) |                 | Min<br>( $t_{CL}(\text{abs}), t_{CH}(\text{abs})$ ) |                 | ps             | 6,13 |

## AC Timing Parameter &amp; Specifications - Contiuned

| Parameter                                                                                   | Symbol      | -1.5             |      | -1.6             |      | Unit           | Note  |

|---------------------------------------------------------------------------------------------|-------------|------------------|------|------------------|------|----------------|-------|

|                                                                                             |             | Min.             | Max. | Min.             | Max. |                |       |

| DQ/DQS output hold time from DQS                                                            | $t_{QH}$    | $t_{HP}-t_{QHS}$ |      | $t_{HP}-t_{QHS}$ |      | ps             |       |

| DQ hold skew factor                                                                         | $t_{QHS}$   |                  | 250  |                  | 250  | ps             |       |

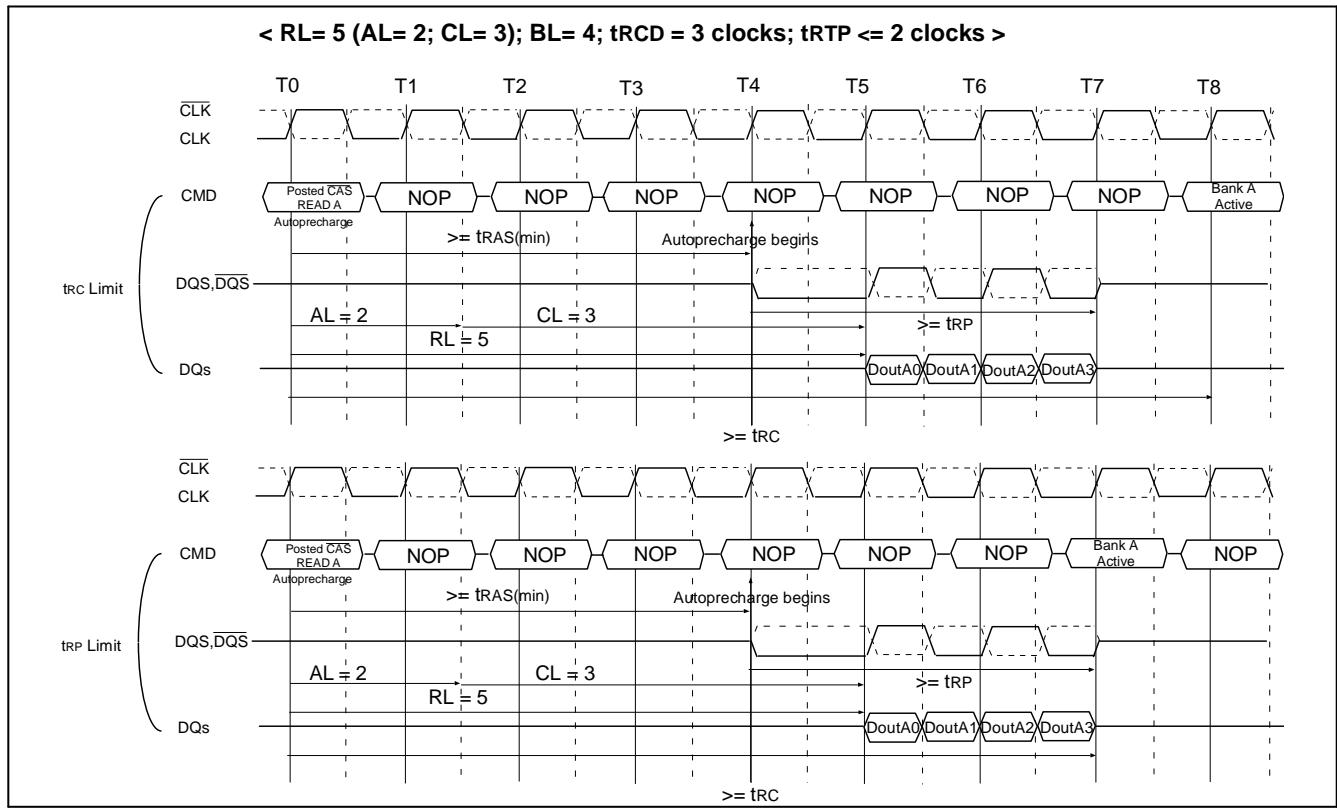

| Active to Precharge command                                                                 | $t_{RAS}$   | 45               | 70K  | 45               | 70K  | ns             |       |

| Active to Active command (same bank)                                                        | $t_{RC}$    | 58.5             |      | 58.35            |      | ns             |       |

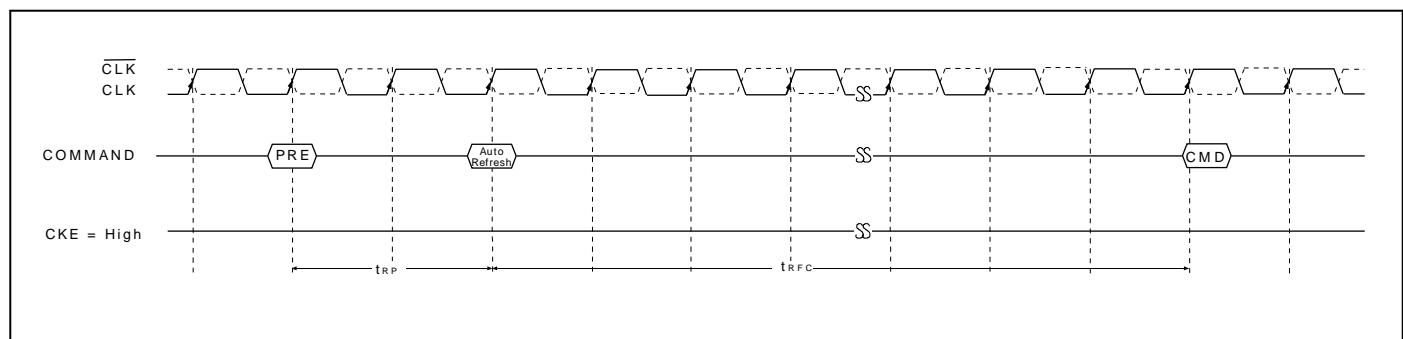

| Auto Refresh row cycle time                                                                 | $t_{RFC}$   | 90               |      | 90               |      | ns             |       |

| Active to Read, Write delay                                                                 | $t_{RCD}$   | 15               |      | 15               |      | ns             |       |

| Precharge command period                                                                    | $t_{RP}$    | 15               |      | 15               |      | ns             |       |

| Active bank A to Active bank B command                                                      | $t_{RRD}$   | 7.5              |      | 8.34             |      | ns             |       |

| Write recovery time                                                                         | $t_{WR}$    | 15               |      | 15               |      | ns             |       |

| Write data in to Read command delay                                                         | $t_{WTR}$   | 7.5              |      | 8.34             |      | ns             | 19    |

| Col. address to Col. address delay                                                          | $t_{CCD}$   | 2                |      | 2                |      | $t_{CK}$       |       |

| Average periodic Refresh interval ( $0^{\circ}\text{C} \leq T_c \leq +85^{\circ}\text{C}$ ) | $t_{REFI}$  |                  | 15.6 |                  | 15.6 | us             |       |

| Average periodic Refresh interval ( $+85^{\circ}\text{C} < T_c \leq +95^{\circ}\text{C}$ )  | $t_{REFI}$  |                  | 7.8  |                  | 7.8  | us             |       |

| Write preamble                                                                              | $t_{WPRE}$  | 0.35             |      | 0.35             |      | $t_{CK}$ (avg) |       |

| Write postamble                                                                             | $t_{WPST}$  | 0.4              | 0.6  | 0.4              | 0.6  | $t_{CK}$ (avg) |       |

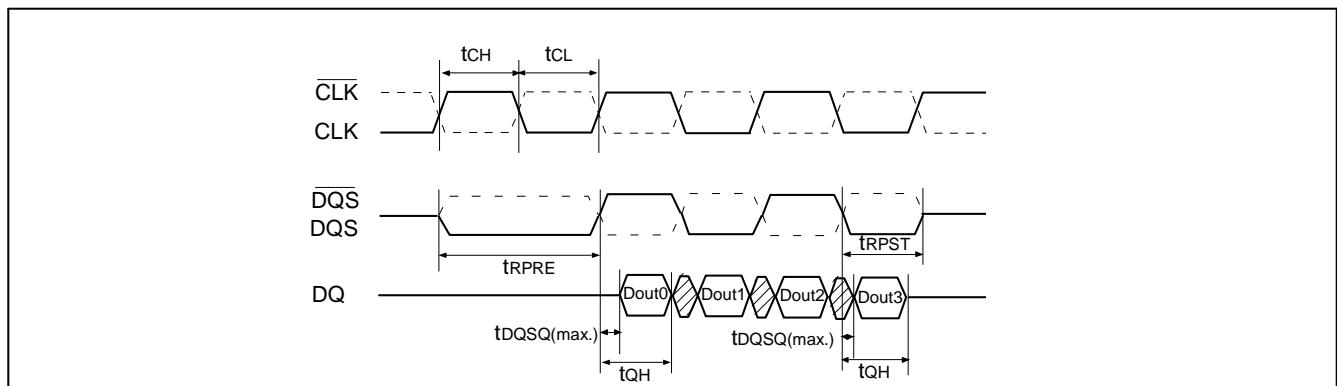

| DQS Read preamble                                                                           | $t_{RPRE}$  | 0.9              | 1.1  | 0.9              | 1.1  | $t_{CK}$ (avg) | 11    |

| DQS Read postamble                                                                          | $t_{RPST}$  | 0.4              | 0.6  | 0.4              | 0.6  | $t_{CK}$ (avg) | 12    |

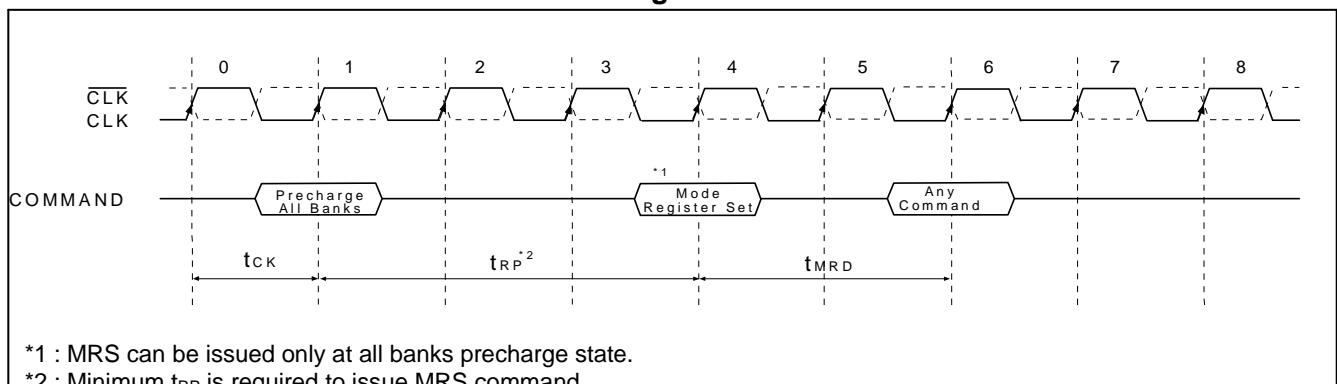

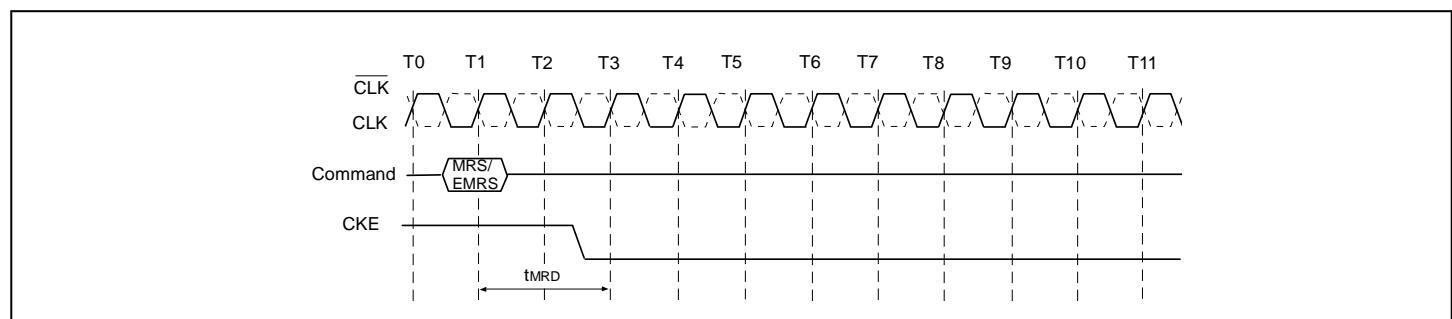

| Load Mode Register / Extended Mode Register cycle time                                      | $t_{MRD}$   | 5                |      | 5                |      | $t_{CK}$       |       |

| Auto Precharge write recovery + Precharge time                                              | $t_{DAL}$   | X                |      | X                |      | $t_{CK}$       | 1, 20 |

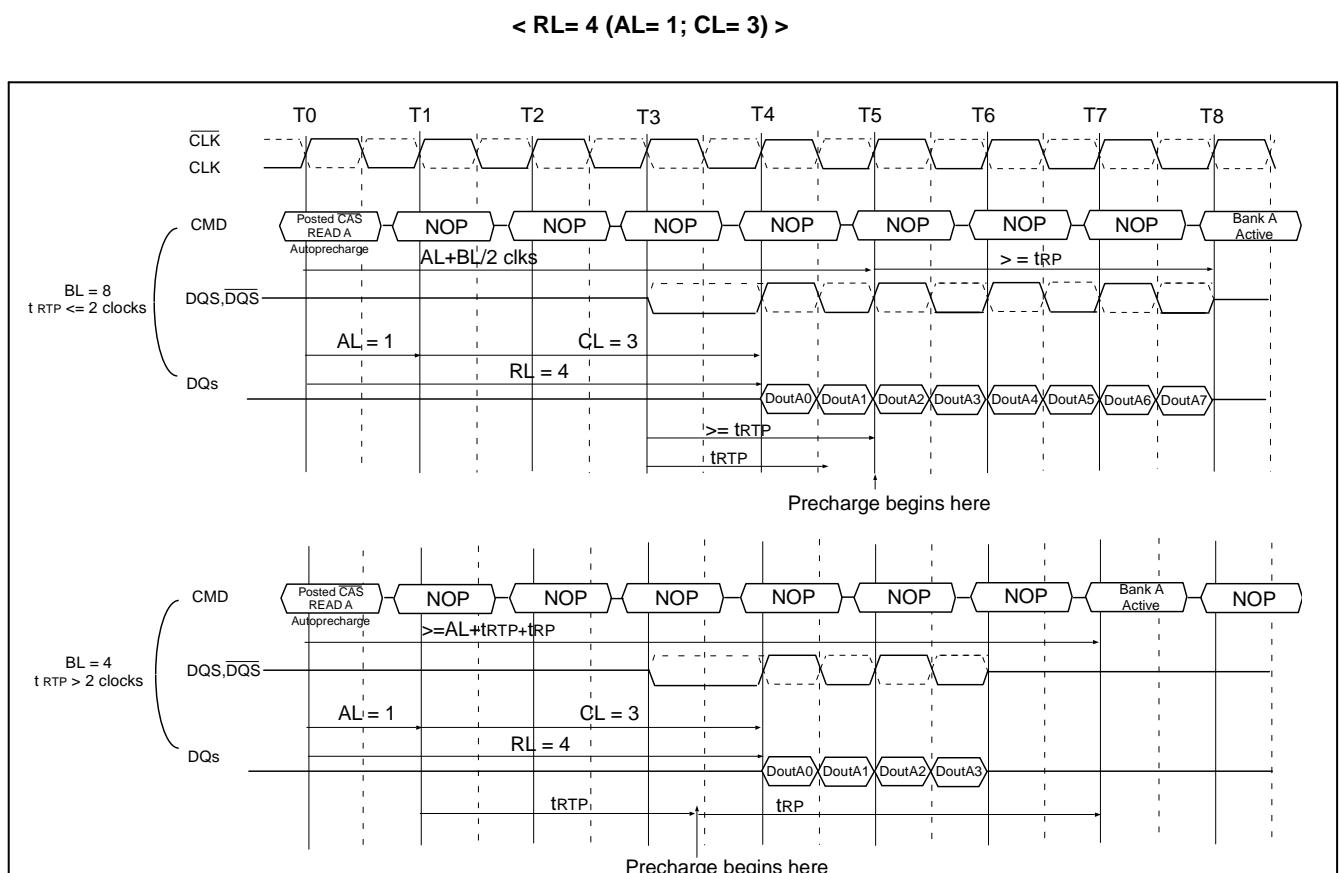

| Internal Read to Precharge command delay                                                    | $t_{RTP}$   | 7.5              |      | 8.34             |      | ns             |       |

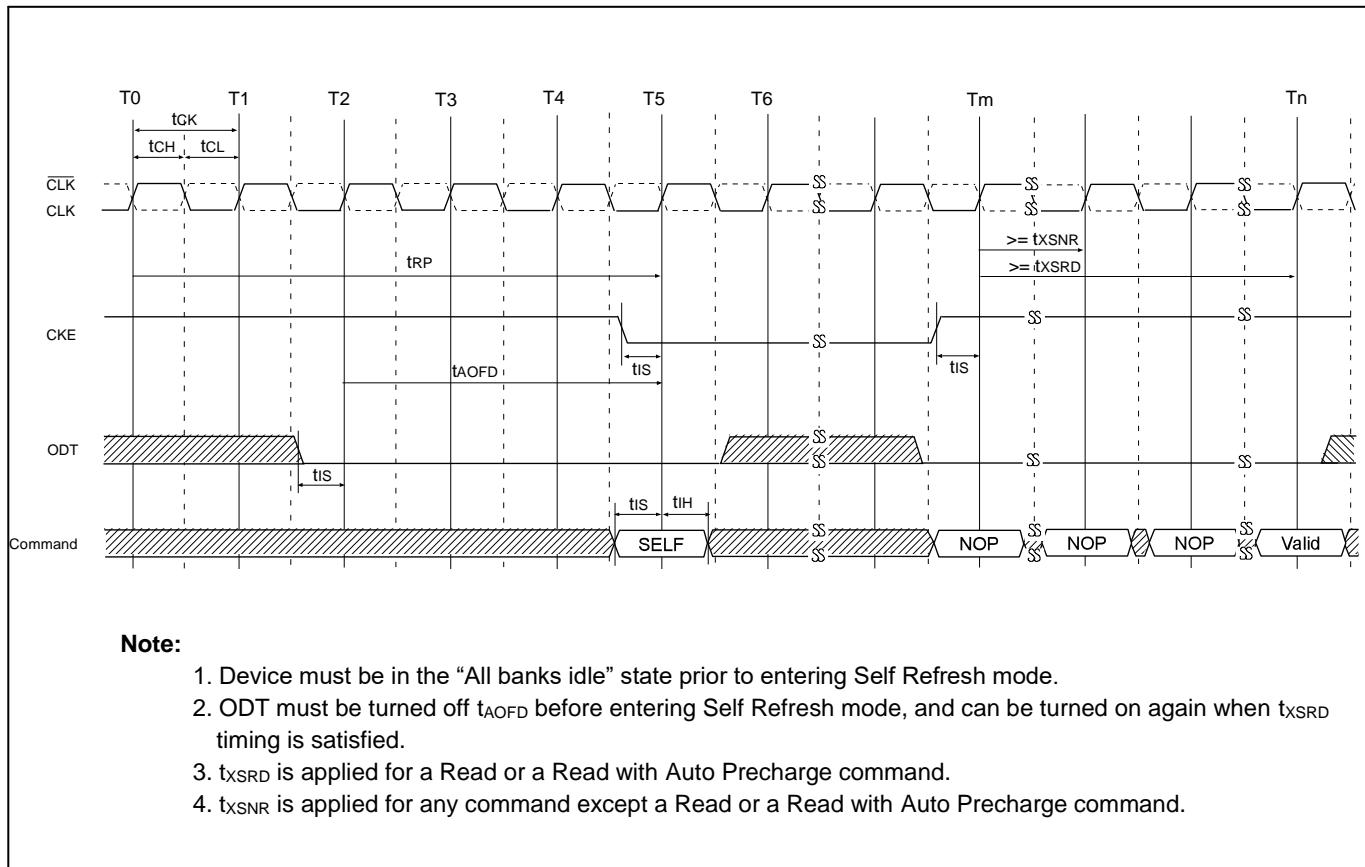

| Exit Self Refresh to Read command                                                           | $t_{XSRD}$  | 200              |      | 200              |      | $t_{CK}$       |       |

| Exit Self Refresh to non-Read command                                                       | $t_{XSNR}$  | $t_{RFC} + 10$   |      | $t_{RFC} + 10$   |      | ns             |       |

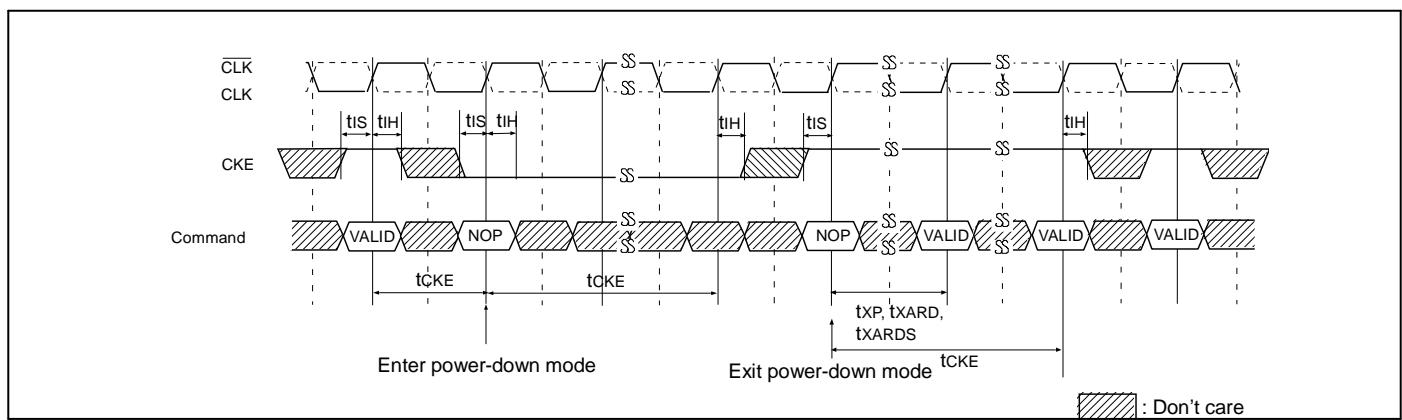

| Exit Precharge Power-Down to any non-Read command                                           | $t_{XP}$    | 5                |      | 5                |      | $t_{CK}$       |       |

| Exit Active Power-Down to Read command                                                      | $t_{XARD}$  | 5                |      | 5                |      | $t_{CK}$       | 3     |

| Exit active power-down to Read command (slow exit / low power mode)                         | $t_{XARDS}$ | 10 - AL          |      | 10 - AL          |      | $t_{CK}$       | 2,3   |

| CKE minimum pulse width (high and low pulse width)                                          | $t_{CKE}$   | 5                |      | 5                |      | $t_{CK}$       |       |

## AC Timing Parameter &amp; Specifications - Contiuued

| Parameter                                                         | Symbol      | -1.5                                 |                                                  | -1.6                                 |                                                  | Unit     | Note         |

|-------------------------------------------------------------------|-------------|--------------------------------------|--------------------------------------------------|--------------------------------------|--------------------------------------------------|----------|--------------|

|                                                                   |             | Min.                                 | Max.                                             | Min.                                 | Max.                                             |          |              |

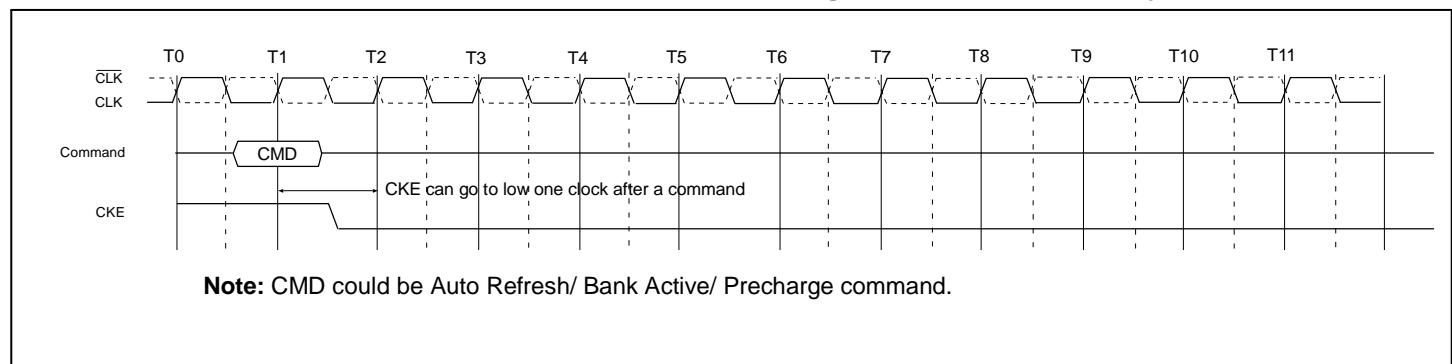

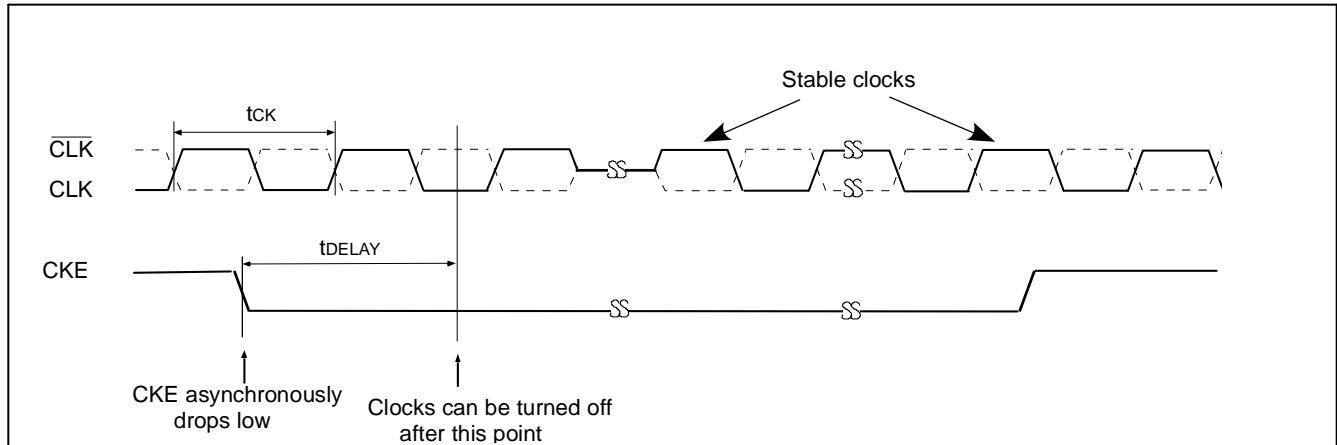

| Minimum time clocks remains ON after CKE asynchronously drops low | $t_{DELAY}$ | $t_{IS} + t_{CK}$<br>(avg)+ $t_{IH}$ |                                                  | $t_{IS} + t_{CK}$<br>(avg)+ $t_{IH}$ |                                                  | ns       |              |

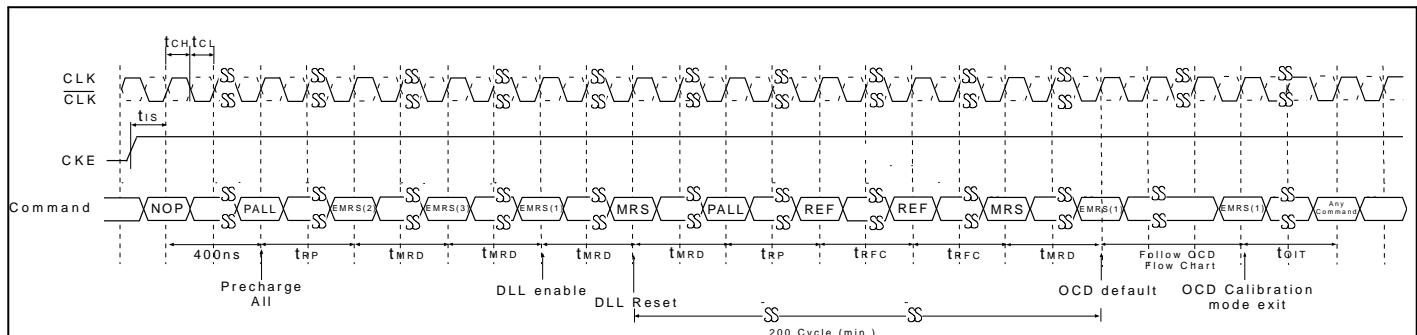

| Output impedance test driver delay                                | $t_{OIT}$   | 0                                    | 12                                               | 0                                    | 12                                               | ns       |              |

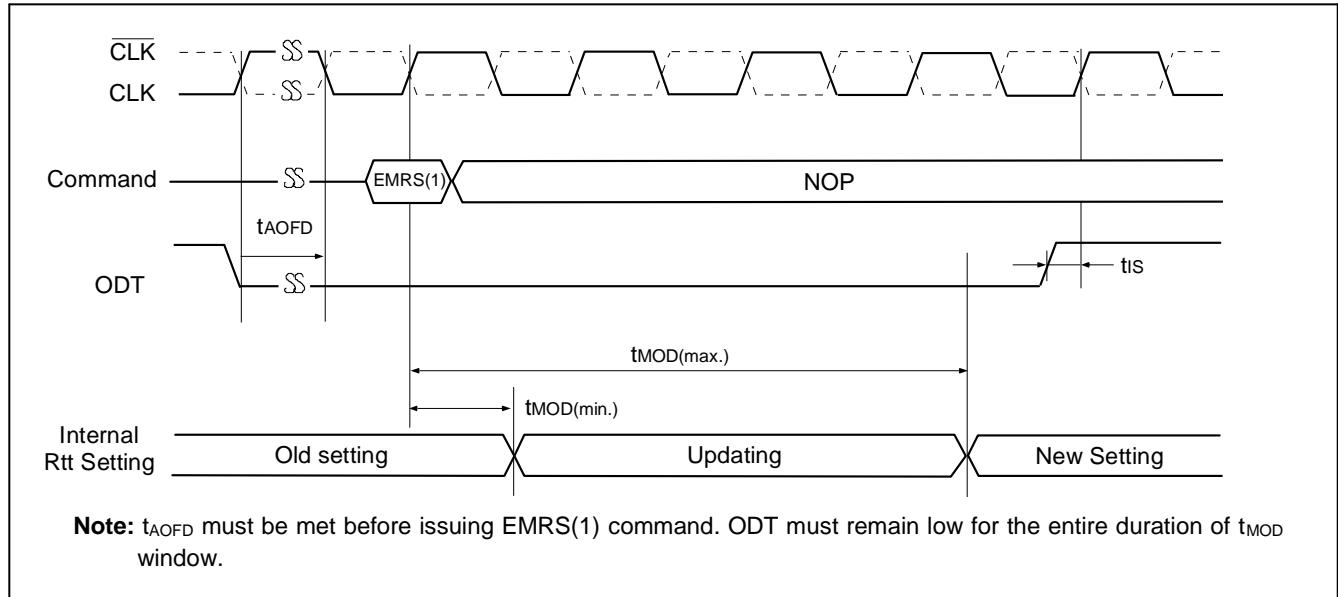

| MRS command to ODT update delay                                   | $t_{MOD}$   | 0                                    | 12                                               | 0                                    | 12                                               | ns       |              |

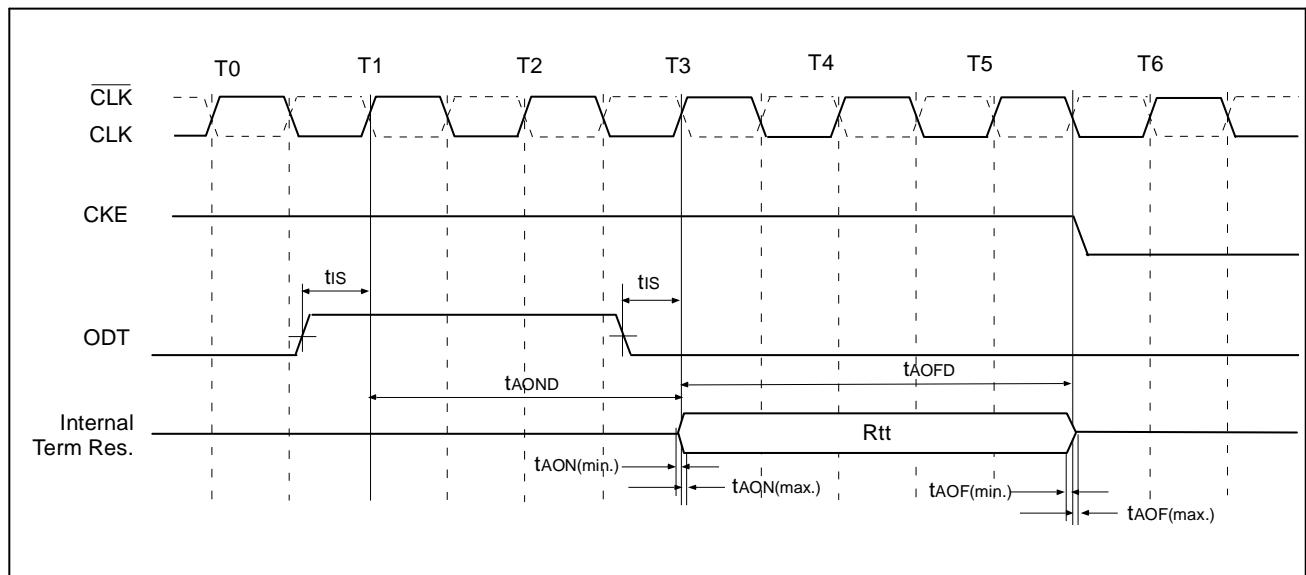

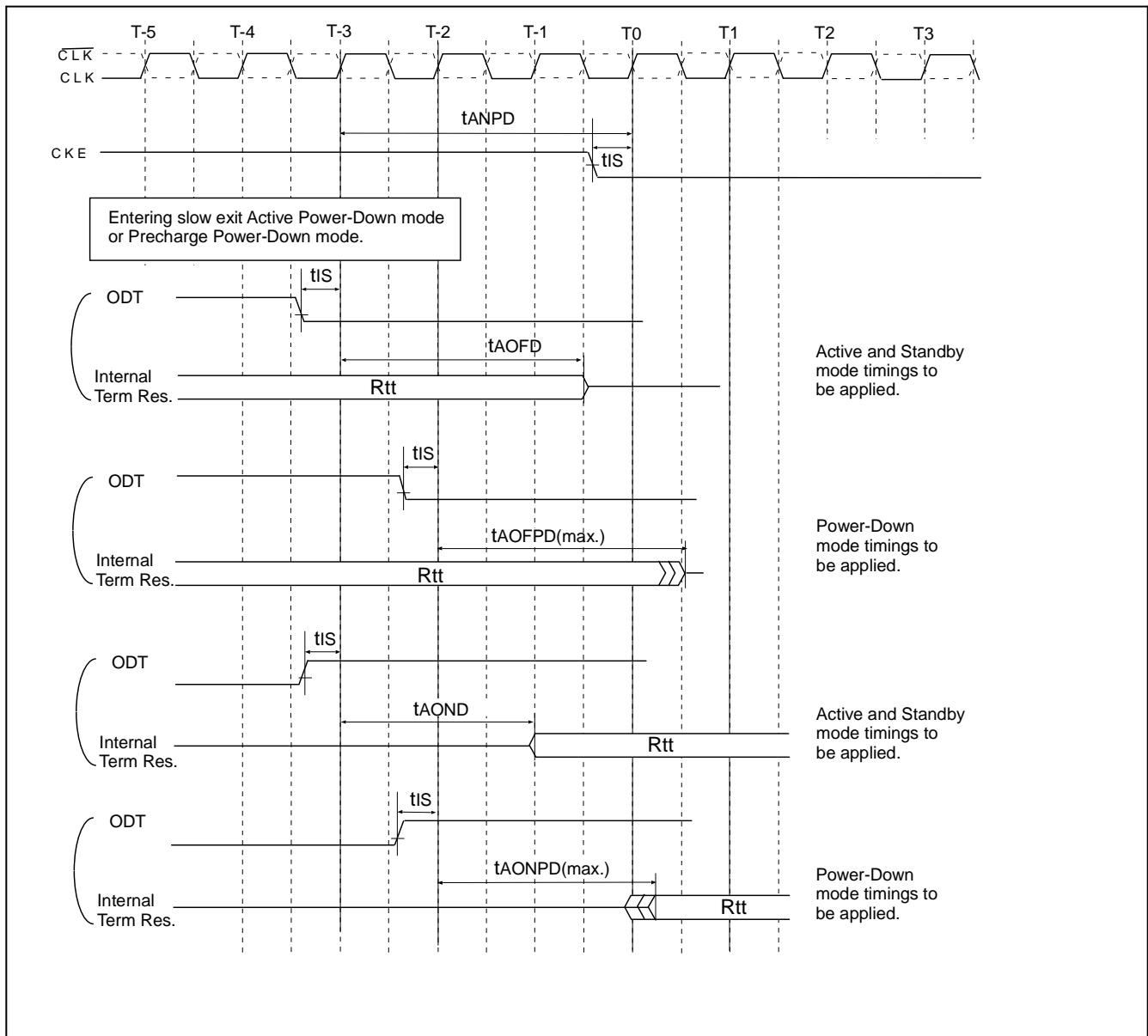

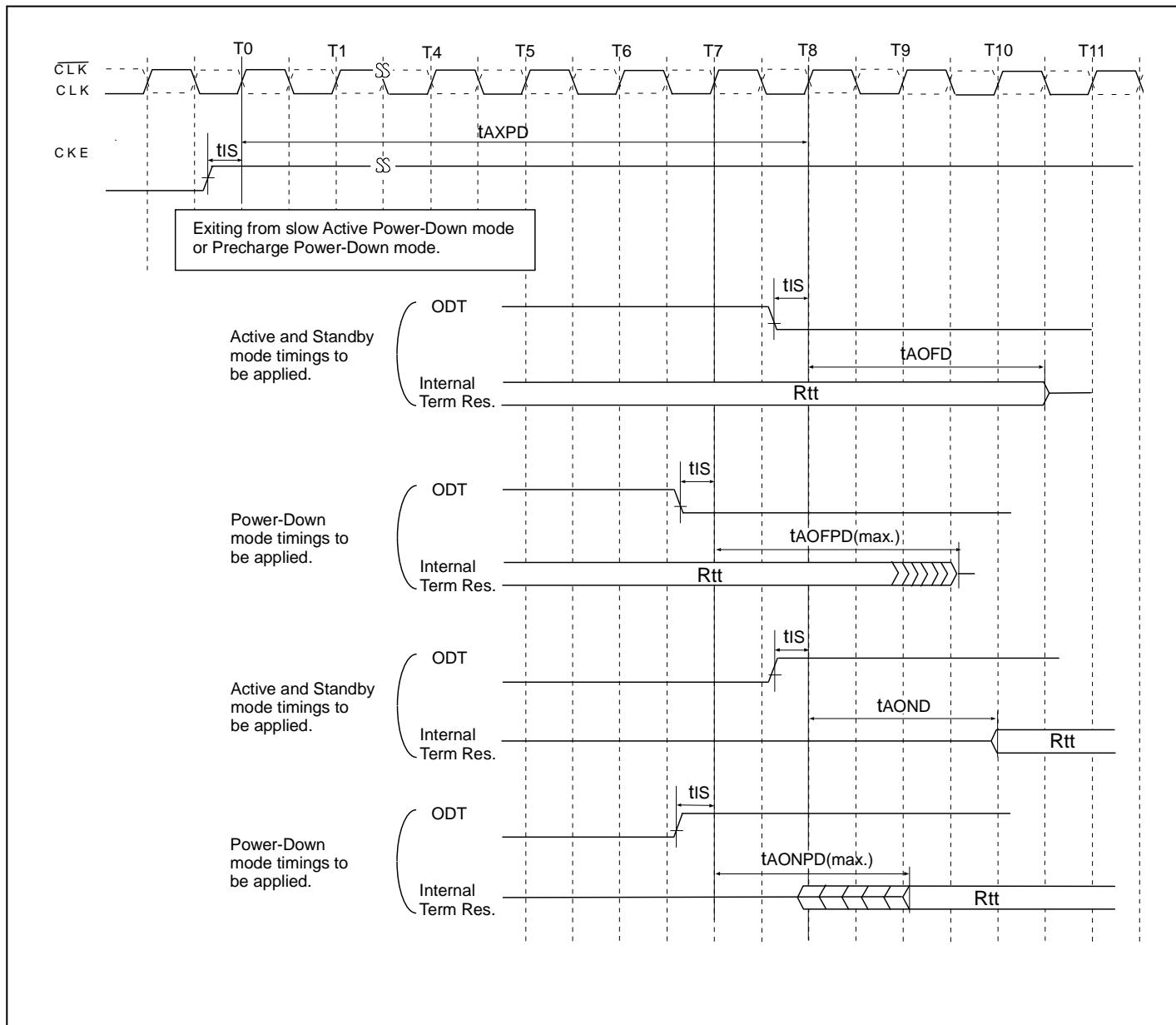

| ODT turn-on delay                                                 | $t_{AOND}$  | 2                                    | 2                                                | 2                                    | 2                                                | $t_{CK}$ |              |

| ODT turn-on                                                       | $t_{AON}$   | $t_{AC}(\text{min.})$                | $t_{AC}(\text{max.}) + 2575$                     | $t_{AC}(\text{min.})$                | $t_{AC}(\text{max.}) + 2575$                     | ps       | 14,16        |

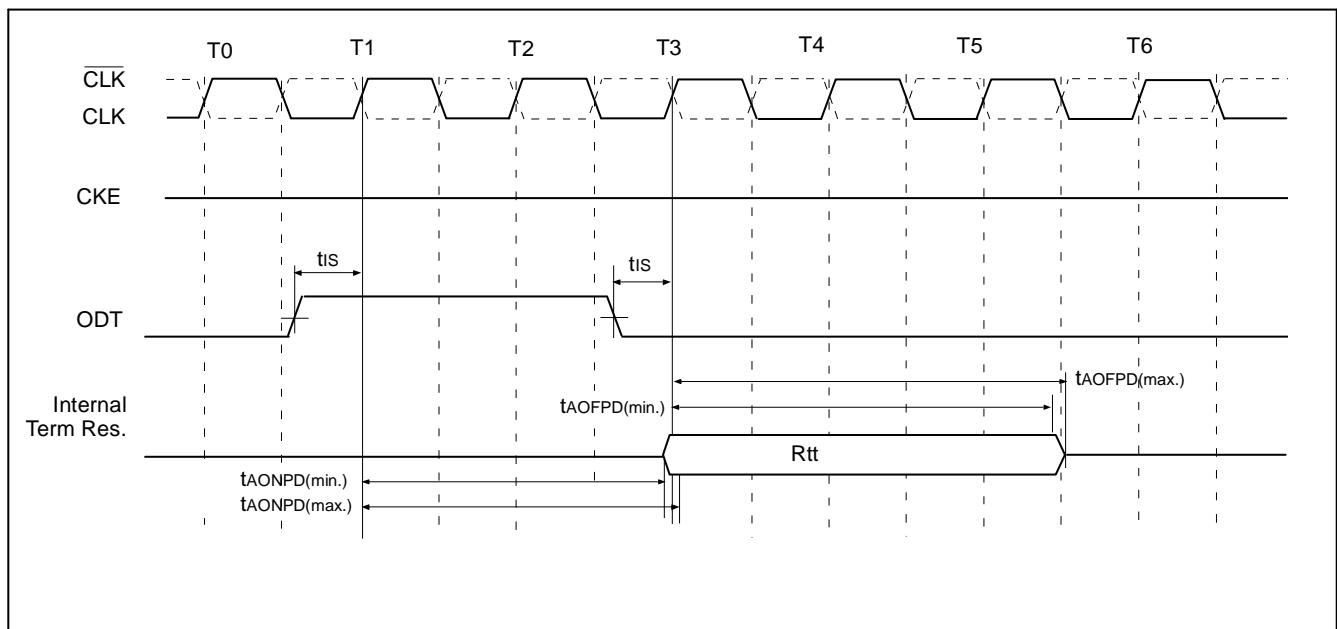

| ODT turn-on (Power-Down mode)                                     | $t_{AONPD}$ | $t_{AC}(\text{min.}) + 2000$         | $3 \times t_{CK} + t_{AC}(\text{max.}) + 1000$   | $t_{AC}(\text{min.}) + 2000$         | $3 \times t_{CK} + t_{AC}(\text{max.}) + 1000$   | ps       |              |

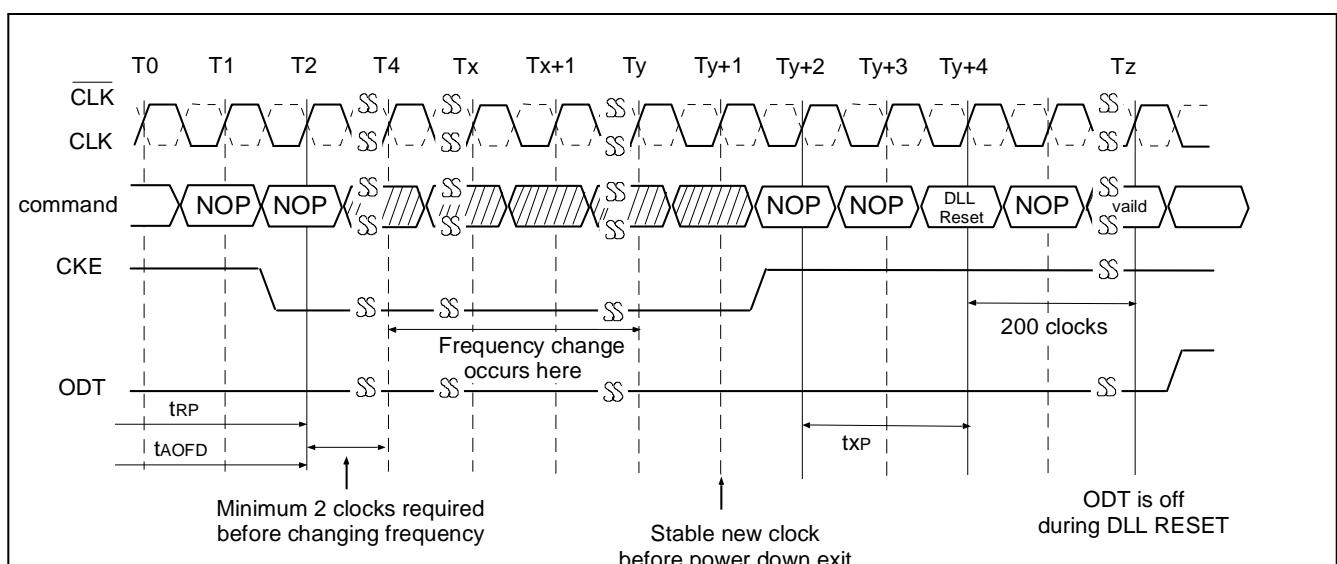

| ODT turn-off delay                                                | $t_{AOFD}$  | 2.5                                  | 2.5                                              | 2.5                                  | 2.5                                              | $t_{CK}$ | 15,17,<br>18 |

| ODT turn-off                                                      | $t_{AOF}$   | $t_{AC}(\text{min.})$                | $t_{AC}(\text{max.}) + 600$                      | $t_{AC}(\text{min.})$                | $t_{AC}(\text{max.}) + 600$                      | ps       |              |

| ODT turn-off (Power-Down mode)                                    | $t_{AOFPD}$ | $t_{AC}(\text{min.}) + 2000$         | $2.5 \times t_{CK} + t_{AC}(\text{max.}) + 1000$ | $t_{AC}(\text{min.}) + 2000$         | $2.5 \times t_{CK} + t_{AC}(\text{max.}) + 1000$ | ps       |              |

| ODT to Power-Down entry latency                                   | $t_{ANPD}$  | 4                                    |                                                  | 4                                    |                                                  | $t_{CK}$ |              |

| ODT Power-Down exit latency                                       | $t_{AXPD}$  | 11                                   |                                                  | 11                                   |                                                  | $t_{CK}$ |              |

## AC Timing Parameter &amp; Specifications - Contiuned

| Parameter                                       | Symbol                 | -1.8                                     |                        | -2.5                                     |                        | Unit                 | Note  |    |

|-------------------------------------------------|------------------------|------------------------------------------|------------------------|------------------------------------------|------------------------|----------------------|-------|----|

|                                                 |                        | Min.                                     | Max.                   | Min.                                     | Max.                   |                      |       |    |

| Clock period                                    | CL=7                   | t <sub>C</sub> (avg)                     | 1875                   | 7500                                     | -                      | -                    | ps    | 12 |

|                                                 | CL=6                   |                                          | 2500                   | 7500                                     | -                      | -                    |       |    |

|                                                 | CL=5                   |                                          | 3000                   | 7500                                     | 2500                   | 8000                 |       |    |

|                                                 | CL=4                   |                                          | 3750                   | 7500                                     | 3750                   | 8000                 |       |    |

| DQ output access time from CLK/<br>CLK          | t <sub>AC</sub>        | -350                                     | +350                   | -400                                     | +400                   | ps                   | 9     |    |

| CLK high-level width                            | t <sub>CH</sub> (avg)  | 0.48                                     | 0.52                   | 0.48                                     | 0.52                   | t <sub>C</sub> (avg) | 12    |    |

| CLK low-level width                             | t <sub>CL</sub> (avg)  | 0.48                                     | 0.52                   | 0.48                                     | 0.52                   | t <sub>C</sub> (avg) | 12    |    |

| DQS output access time from CLK/<br>CLK         | t <sub>DQSCK</sub>     | -325                                     | +325                   | -350                                     | +350                   | ps                   | 9     |    |

| Clock to first rising edge of DQS delay         | t <sub>DQSS</sub>      | -0.25                                    | +0.25                  | -0.25                                    | +0.25                  | t <sub>C</sub> (avg) |       |    |

| Data-in and DM setup time (to DQS)              | t <sub>DS</sub> (base) | 0                                        |                        | 50                                       |                        | ps                   | 3     |    |

| Data-in and DM hold time (to DQS)               | t <sub>DH</sub> (base) | 75                                       |                        | 125                                      |                        | ps                   | 4     |    |

| DQ and DM input pulse width (for<br>each input) | t <sub>DIPW</sub>      | 0.35                                     |                        | 0.35                                     |                        | t <sub>C</sub> (avg) |       |    |

| Address and Control Input setup time            | t <sub>IS</sub> (base) | 125                                      |                        | 175                                      |                        | ps                   | 3     |    |

| Address and Control Input hold time             | t <sub>IH</sub> (base) | 200                                      |                        | 250                                      |                        | ps                   | 4     |    |

| Control and Address input pulse width           | t <sub>IPW</sub>       | 0.6                                      |                        | 0.6                                      |                        | t <sub>C</sub> (avg) |       |    |

| DQS input high pulse width                      | t <sub>DQSH</sub>      | 0.35                                     |                        | 0.35                                     |                        | t <sub>C</sub> (avg) |       |    |

| DQS input low pulse width                       | t <sub>DQSL</sub>      | 0.35                                     |                        | 0.35                                     |                        | t <sub>C</sub> (avg) |       |    |

| DQS falling edge to CLK rising setup<br>time    | t <sub>DSS</sub>       | 0.2                                      |                        | 0.2                                      |                        | t <sub>C</sub> (avg) |       |    |

| DQS falling edge from CLK rising hold<br>time   | t <sub>DSH</sub>       | 0.2                                      |                        | 0.2                                      |                        | t <sub>C</sub> (avg) |       |    |

| Data strobe edge to output data edge            | t <sub>DQSQ</sub>      |                                          | 175                    |                                          | 200                    | ps                   |       |    |

| Data-out high-impedance window from<br>CLK/CLK  | t <sub>HZ</sub>        |                                          | t <sub>AC</sub> (max.) |                                          | t <sub>AC</sub> (max.) | ps                   | 9     |    |

| Data-out low-impedance window from<br>CLK/CLK   | t <sub>LZ</sub> (DQS)  | t <sub>AC</sub> (min.)                   | t <sub>AC</sub> (max.) | t <sub>AC</sub> (min.)                   | t <sub>AC</sub> (max.) | ps                   | 9     |    |

| DQ low-impedance window from CLK/<br>CLK        | t <sub>LZ</sub> (DQ)   | 2 x t <sub>AC</sub> (min.)               | t <sub>AC</sub> (max.) | 2 x t <sub>AC</sub> (min.)               | t <sub>AC</sub> (max.) | ps                   | 9     |    |

| Half clock period                               | t <sub>HP</sub>        | Min (t <sub>CL</sub> , t <sub>CH</sub> ) |                        | Min (t <sub>CL</sub> , t <sub>CH</sub> ) |                        | ps                   | 5, 12 |    |

| DQ/DQS output hold time from DQS                | t <sub>QH</sub>        | t <sub>HP</sub> -t <sub>QHS</sub>        |                        | t <sub>HP</sub> -t <sub>QHS</sub>        |                        | ps                   |       |    |

| DQ hold skew factor                             | t <sub>QHS</sub>       |                                          | 250                    |                                          | 300                    | ps                   |       |    |

## AC Timing Parameter &amp; Specifications - Continued

| Parameter                                                           | Symbol             | -1.8                                                      |      | -2.5                                                      |      | Unit                  | Note |

|---------------------------------------------------------------------|--------------------|-----------------------------------------------------------|------|-----------------------------------------------------------|------|-----------------------|------|

|                                                                     |                    | Min.                                                      | Max. | Min.                                                      | Max. |                       |      |

| Active to Precharge command                                         | t <sub>RAS</sub>   | 40                                                        | 70K  | 45                                                        | 70K  | ns                    |      |

| Active to Active command (same bank)                                | t <sub>RC</sub>    | 58.125                                                    |      | 57.5                                                      |      | ns                    |      |

| Auto Refresh row cycle time                                         | t <sub>RFC</sub>   | 75                                                        |      | 75                                                        |      | ns                    |      |

| Active to Read, Write delay                                         | t <sub>RCD</sub>   | 13.125                                                    |      | 12.5                                                      |      | ns                    |      |

| Precharge command period                                            | t <sub>RP</sub>    | 13.125                                                    |      | 12.5                                                      |      | ns                    |      |

| Active bank A to Active bank B command (1KB page size)              | t <sub>RRD</sub>   | 7.5                                                       |      | 7.5                                                       |      | ns                    |      |

| Write recovery time                                                 | t <sub>WR</sub>    | 15                                                        |      | 15                                                        |      | ns                    |      |

| Write data in to Read command delay                                 | t <sub>WTR</sub>   | 7.5                                                       |      | 7.5                                                       |      | ns                    | 19   |

| Col. address to Col. address delay                                  | t <sub>CCD</sub>   | 2                                                         |      | 2                                                         |      | t <sub>Ck</sub>       |      |

| Average periodic Refresh interval (0°C ≤ T <sub>c</sub> ≤ +85°C)    | t <sub>REFI</sub>  |                                                           | 15.6 |                                                           | 15.6 | μs                    |      |

| Average periodic Refresh interval (+85°C < T <sub>c</sub> ≤ +95°C)  | t <sub>REFI</sub>  |                                                           | 7.8  |                                                           | 7.8  | μs                    |      |

| Write preamble                                                      | t <sub>WPRE</sub>  | 0.35                                                      |      | 0.35                                                      |      | t <sub>Ck</sub> (avg) |      |

| Write postamble                                                     | t <sub>WPST</sub>  | 0.4                                                       | 0.6  | 0.4                                                       | 0.6  | t <sub>Ck</sub> (avg) |      |

| DQS Read preamble                                                   | t <sub>RPRE</sub>  | 0.9                                                       | 1.1  | 0.9                                                       | 1.1  | t <sub>Ck</sub> (avg) | 10   |

| DQS Read postamble                                                  | t <sub>RPST</sub>  | 0.4                                                       | 0.6  | 0.4                                                       | 0.6  | t <sub>Ck</sub> (avg) | 11   |

| Load Mode Register / Extended Mode Register cycle time              | t <sub>MRD</sub>   | 2                                                         |      | 2                                                         |      | t <sub>Ck</sub>       |      |

| Auto Precharge write recovery + Precharge time                      | t <sub>DAL</sub>   | WR + t <sub>nRP</sub>                                     |      | WR + t <sub>nRP</sub>                                     |      | t <sub>Ck</sub>       | 18   |

| Internal Read to Precharge command delay                            | t <sub>RTP</sub>   | 7.5                                                       |      | 7.5                                                       |      | ns                    |      |

| Exit Self Refresh to Read command                                   | t <sub>XSRD</sub>  | 200                                                       |      | 200                                                       |      | t <sub>Ck</sub>       |      |

| Exit Self Refresh to non-Read command                               | t <sub>XSNR</sub>  | t <sub>RFC</sub> + 10                                     |      | t <sub>RFC</sub> + 10                                     |      | ns                    |      |

| Exit Precharge Power-Down to any non-Read command                   | t <sub>XP</sub>    | 3                                                         |      | 2                                                         |      | t <sub>Ck</sub>       |      |

| Exit Active Power-Down to Read command                              | t <sub>XARD</sub>  | 3                                                         |      | 2                                                         |      | t <sub>Ck</sub>       | 2    |

| Exit active power-down to Read command (slow exit / low power mode) | t <sub>XARDS</sub> | 10 - AL                                                   |      | 8 - AL                                                    |      | t <sub>Ck</sub>       | 1,2  |

| CKE minimum pulse width (high and low pulse width)                  | t <sub>CKE</sub>   | 3                                                         |      | 3                                                         |      | t <sub>Ck</sub>       |      |

| Minimum time clocks remains ON after CKE asynchronously drops low   | t <sub>DELAY</sub> | t <sub>IS</sub> + t <sub>Ck</sub> (avg) + t <sub>IH</sub> |      | t <sub>IS</sub> + t <sub>Ck</sub> (avg) + t <sub>IH</sub> |      | ns                    |      |

## AC Timing Parameter &amp; Specifications - Continued

| Parameter                          | Symbol      | -1.8                            |                                                                | -2.5                      |                                                                | Unit            | Note         |

|------------------------------------|-------------|---------------------------------|----------------------------------------------------------------|---------------------------|----------------------------------------------------------------|-----------------|--------------|

|                                    |             | Min.                            | Max.                                                           | Min.                      | Max.                                                           |                 |              |

| Output impedance test driver delay | $t_{OIT}$   | 0                               | 12                                                             | 0                         | 12                                                             | ns              |              |

| MRS command to ODT update delay    | $t_{MOD}$   | 0                               | 12                                                             | 0                         | 12                                                             | ns              |              |

| ODT turn-on delay                  | $t_{AOND}$  | 2                               | 2                                                              | 2                         | 2                                                              | t <sub>Ck</sub> |              |

| ODT turn-on                        | $t_{AON}$   | $t_{AC}(\text{min.})$<br>+2.575 | $t_{AC}(\text{max.})$<br>+2.575                                | $t_{AC}(\text{min.})$     | $t_{AC}(\text{max.}) + 0.7$                                    | ns              | 13,15        |

| ODT turn-on (Power-Down mode)      | $t_{AONPD}$ | $t_{AC}(\text{min.}) + 2$       | $3 \times t_{Ck}(\text{avg})$<br>+ $t_{AC}(\text{max.}) + 1$   | $t_{AC}(\text{min.}) + 2$ | $2 \times t_{Ck}(\text{avg})$<br>+ $t_{AC}(\text{max.}) + 1$   | ns              |              |

| ODT turn-off delay                 | $t_{AOFD}$  | 2.5                             | 2.5                                                            | 2.5                       | 2.5                                                            | t <sub>Ck</sub> | 14,<br>16,17 |

| ODT turn-off                       | $t_{AOF}$   | $t_{AC}(\text{min.})$           | $t_{AC}(\text{max.}) + 0.6$                                    | $t_{AC}(\text{min.})$     | $t_{AC}(\text{max.}) + 0.6$                                    | ns              |              |

| ODT turn-off (Power-Down mode)     | $t_{AOFPD}$ | $t_{AC}(\text{min.}) + 2$       | $2.5 \times t_{Ck}(\text{avg})$<br>+ $t_{AC}(\text{max.}) + 1$ | $t_{AC}(\text{min.}) + 2$ | $2.5 \times t_{Ck}(\text{avg})$<br>+ $t_{AC}(\text{max.}) + 1$ | ns              |              |

| ODT to Power-Down entry latency    | $t_{ANPD}$  | 4                               |                                                                | 3                         |                                                                | t <sub>Ck</sub> |              |

| ODT Power-Down exit latency        | $t_{AXPD}$  | 11                              |                                                                | 8                         |                                                                | t <sub>Ck</sub> |              |

## Note:

1. AL: Additive Latency.

2. MRS A12 bit defines which Active Power-Down Exit timing to be applied.

3. The figures of Input Waveform Timing 1 and 2 are referenced from the input signal crossing at the  $V_{IH}$  (AC) level for a rising signal and  $V_{IL}$  (AC) for a falling signal applied to the device under test.

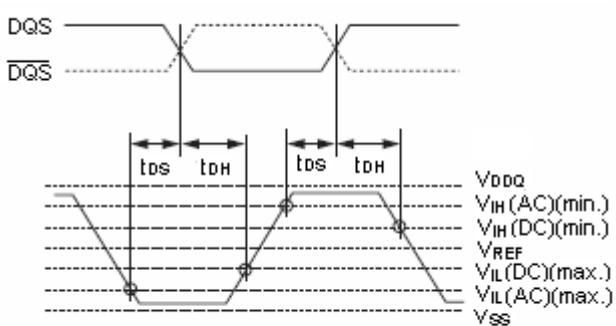

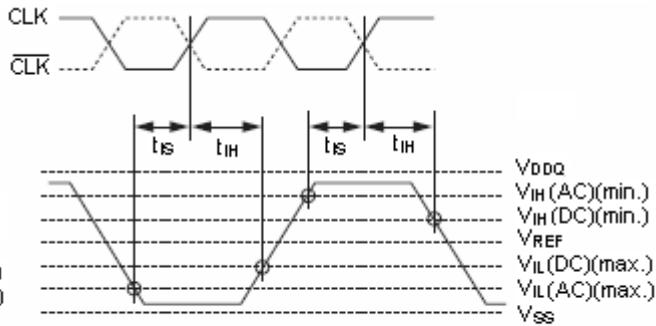

4. The figures of Input Waveform Timing 1 and 2 are referenced from the input signal crossing at the  $V_{IL}$  (DC) level for a rising signal and  $V_{IH}$  (DC) for a falling signal applied to the device under test.

Input Waveform Timing 1 (t<sub>DS</sub>, t<sub>DH</sub>)Input Waveform Timing 2 (t<sub>IS</sub>, t<sub>IH</sub>)

5. t<sub>HP</sub> is the minimum of the absolute half period of the actual input clock. t<sub>HP</sub> is an input parameter but not an input specification parameter. It is used in conjunction with t<sub>QHS</sub> to derive the DRAM output timing t<sub>QH</sub>. The value to be used for t<sub>QH</sub> calculation is determined by the following equation;

$$t_{HP} = \text{Min} ( t_{CH}(\text{abs}), t_{CL}(\text{abs}) ),$$

where:

$t_{CH}(\text{abs})$  is the minimum of the actual instantaneous clock HIGH time;

$t_{CL}(\text{abs})$  is the minimum of the actual instantaneous clock LOW time;

6. t<sub>QHS</sub> accounts for:

- The pulse duration distortion of on-chip clock circuits, which represents how well the actual t<sub>HP</sub> at the input is transferred to the output; and

- The worst case push-out of DQS on one transition followed by the worst case pull-in of DQ on the next transition, both of which are independent of each other, due to data pin skew, output pattern effects, and p-channel to n-channel variation of the output drivers.

7.  $t_{QH} = t_{HP} - t_{QHS}$ , where:

$t_{HP}$  is the minimum of the absolute half period of the actual input clock; and  $t_{QHS}$  is the specification value under the max column. {The less half-pulse width distortion present, the larger the  $t_{QH}$  value is; and the larger the valid data eye will be.}

Examples:

a. If the system provides  $t_{HP}$  of 1200 ps into a DDR2-800 SDRAM, the DRAM provides  $t_{QH}$  of 900 ps minimum.

b. If the system provides  $t_{HP}$  of 1300 ps into a DDR2-800 SDRAM, the DRAM provides  $t_{QH}$  of 1000 ps minimum.

8. RU stands for round up. WR refers to the  $t_{WR}$  parameter stored in the MRS.

9. When the device is operated with input clock jitter, this parameter needs to be de-rated by the actual  $t_{ERR}$  (6-10per) of the input clock. (output de-ratings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-800 SDRAM has  $t_{ERR}$  (6-10per)(min.) = - 272 ps and  $t_{ERR}$  (6-10per)(max.) = + 293 ps, then  $t_{DQSCK}$  (min.)(derated) =  $t_{DQSCK}$  (min.) -  $t_{ERR}$  (6-10per)(max.) = -350 ps - 293 ps = -643 ps and  $t_{DQSCK}$  (max.)(derated) =  $t_{DQSCK}$  (max.) -  $t_{ERR}$  (6-10per)(min.) = 350 ps + 272 ps = +622 ps. Similarly,  $t_{LZ}$  (DQ) for DDR2-800 de-rates to  $t_{LZ}$  (DQ)(min.)(derated) = -800 ps - 293 ps = -1093 ps and  $t_{LZ}$  (DQ)(max.)(derated) = 400 ps + 272 ps = +672 ps.

10. When the device is operated with input clock jitter, this parameter needs to be de-rated by the actual  $t_{JIT}$  (per) of the input clock. (output de-ratings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-800 SDRAM has  $t_{JIT}$  (per)(min.) = - 72 ps and  $t_{JIT}$  (per)(max.) = + 93 ps, then  $t_{RPRE}$  (min.)(derated) =  $t_{RPRE}$  (min.) +  $t_{JIT}$  (per)(min.) = 0.9 x  $t_{CK}$  (avg) - 72 ps = + 2178 ps and  $t_{RPRE}$  (max.)(derated) =  $t_{RPRE}$  (max.) +  $t_{JIT}$  (per)(max.) = 1.1 x  $t_{CK}$  (avg) + 93 ps = + 2843 ps.

11. When the device is operated with input clock jitter, this parameter needs to be de-rated by the actual  $t_{JIT}$  (duty) of the input clock. (output de-ratings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-800 SDRAM has  $t_{JIT}$  (duty)(min.) = - 72 ps and  $t_{JIT}$  (duty)(max.) = + 93 ps, then  $t_{RPST}$  (min.)(derated) =  $t_{RPST}$  (min.) +  $t_{JIT}$  (duty)(min.) = 0.4 x  $t_{CK}$  (avg) - 72 ps = + 928 ps and  $t_{RPST}$  (max.)(derated) =  $t_{RPST}$  (max.) +  $t_{JIT}$  (duty)(max.) = 0.6 x  $t_{CK}$  (avg) + 93 ps = + 1593 ps.

12. Refer to the Clock Jitter table.

13. ODT turn on time min is when the device leaves high impedance and ODT resistance begins to turn on.

ODT turn on time max is when the ODT resistance is fully on. Both are measured from  $t_{AOOND}$ .

14. ODT turn off time min is when the device starts to turn off ODT resistance.

ODT turn off time max is when the bus is in high impedance. Both are measured from  $t_{AOOFD}$ .

15. When the device is operated with input clock jitter, this parameter needs to be de-rated by the actual  $t_{ERR}$  (6-10per) of the input clock. (output de-ratings are relative to the SDRAM input clock.)

16. When the device is operated with input clock jitter, this parameter needs to be derated by  $\{ - t_{JIT}(\text{duty})(\text{max.}) - t_{ERR}$  (6-10per)(max.} and  $\{ - t_{JIT}(\text{duty})(\text{min.}) - t_{ERR}$  (6-10per)(min.} of the actual input clock. (output deratings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-800 SDRAM has  $t_{ERR}$  (6-10per)(min.) = - 272 ps,  $t_{ERR}$  (6-10per)(max.) = + 293 ps,  $t_{JIT}$  (duty)(min.) = -96 ps and  $t_{JIT}$  (duty)(max.) = + 94 ps, then  $t_{AOF}$ (min.)(derated) =  $t_{AOF}$ (min.) +  $\{ - t_{JIT}(\text{duty})(\text{max.}) - t_{ERR}$  (6-10per)(max.} = -400 ps +  $\{ - 94 \text{ ps} - 293 \text{ ps} \} = -787 \text{ ps}$  and  $t_{AOF}$ (max.)(derated) =  $t_{AOF}$ (max.) +  $\{ - t_{JIT}(\text{duty})(\text{min.}) - t_{ERR}$  (6-10per)(min.} = 1000 ps +  $\{ 96 \text{ ps} + 272 \text{ ps} \} = +1368 \text{ ps}$ .

17. For  $t_{AOFD}$  of DDR2-800/1066, the 1/2 clock of  $t_{CK}$  in the  $2.5 \times t_{CK}$  assumes a  $t_{CH}$  (avg), average input clock HIGH pulse width of 0.5 relative to  $t_{CK}$  (avg).  $t_{AOF}$  (min.) and  $t_{AOF}$  (max.) should each be derated by the same amount as the actual amount of  $t_{CH}$  (avg) offset present at the DRAM input with respect to 0.5.

For example, if an input clock has a worst case  $t_{CH}$  (avg) of 0.48, the  $t_{AOF}$  (min.) should be derated by subtracting  $0.02 \times t_{CK}$  (avg) from it, whereas if an input clock has a worst case  $t_{CH}$  (avg) of 0.52, the  $t_{AOF}$  (max.) should be derated by adding  $0.02 \times t_{CK}$  (avg) to it. Therefore, we have;

$t_{AOF}$  (min.)(derated) =  $t_{AC}$  (min.) -  $[0.5 - \text{Min}(0.5, t_{CH}(\text{avg})(\text{min.}))] \times t_{CK}$  (avg)

$t_{AOF}$  (max.)(derated) =  $t_{AC}$  (max.) +  $0.6 + [\text{Max}(0.5, t_{CH}(\text{avg})(\text{max.})) - 0.5] \times t_{CK}$  (avg)

or

$t_{AOF}$  (min.)(derated) =  $\text{Min}(t_{AC}(\text{min.}), t_{AC}(\text{min.}) - [0.5 - t_{CH}(\text{avg})(\text{min.})] \times t_{CK}(\text{avg}))$

$t_{AOF}$  (max.)(derated) =  $0.6 + \text{Max}(t_{AC}(\text{max.}), t_{AC}(\text{max.}) + [t_{CH}(\text{avg})(\text{max.}) - 0.5] \times t_{CK}(\text{avg}))$ , where:

$t_{CH}$  (avg)(min.) and  $t_{CH}$  (avg)(max.) are the minimum and maximum of  $t_{CH}$  (avg) actually measured at the DRAM input balls.

18.  $t_{DAL}$  [nCLK] = WR [nCLK] +  $t_{nRP}$  [nCLK] = WR + RU  $\{t_{RP}$  [ps] /  $t_{CK}$  (avg) [ps], where WR is the value programmed in the mode register set.

19.  $t_{WTR}$  is at least two clocks (2 x tCK or 2 x nCK) independent of operation frequency.

20. If  $t_{CK} < 1.875\text{ns}$ , the device can not support Write with Auto Precharge function.

## ODT DC Electrical Characteristics

| Parameter                                                                        | Symbol      | Min. | Typ. | Max. | Unit     |

|----------------------------------------------------------------------------------|-------------|------|------|------|----------|

| Rtt effective impedance value for $75\Omega$ setting<br>EMRS(1) [A6, A2] = 0, 1  | Rtt1(eff)   | 60   | 75   | 90   | $\Omega$ |

| Rtt effective impedance value for $150\Omega$ setting<br>EMRS(1) [A6, A2] = 1, 0 | Rtt2(eff)   | 120  | 150  | 180  | $\Omega$ |

| Rtt effective impedance value for $50\Omega$ setting<br>EMRS(1) [A6, A2] = 1, 1  | Rtt3(eff)   | 40   | 50   | 60   | $\Omega$ |

| Deviation of VM with respect to $V_{DDQ}/2$                                      | $\Delta VM$ | -6   | -    | +6   | %        |

## Note:

Measurement Definition for Rtt(eff) :

Rtt(eff) is determined by separately applying  $V_{IH}(AC)$  and  $V_{IL}(AC)$  to test pin, and then measuring current  $I(V_{IH}(AC))$  and  $I(V_{IL}(AC))$  respectively.

$$Rtt(eff) = \frac{V_{IH}(AC) - V_{IL}(AC)}{I(V_{IH}(AC)) - I(V_{IL}(AC))}$$

Measurement Definition for  $\Delta VM$  :

Measure voltage (VM) at test pin with no load.

$$\Delta VM = \left( \frac{2 \times VM}{V_{DDQ}} - 1 \right) \times 100\%$$

## OCD Default Characteristics

| Parameter                      | Min. | Typ. | Max. | Unit     | Note  |

|--------------------------------|------|------|------|----------|-------|

| Output impedance               | 12.6 | 18   | 23.4 | $\Omega$ | 1     |

| Pull-up and pull-down mismatch | 0    | -    | 4    | $\Omega$ | 1,2,3 |

| Output slew rate               | 1.5  | -    | 5    | V/ns     | 1,4,5 |

## Note:

1. Absolute specifications: the operation range of Voltage and Temperature.

2. Impedance measurement condition for output source DC current:  $V_{DDQ} = 1.7V$ ;  $V_{OUT} = 1,420mV$ ;  $(V_{OUT} - V_{DDQ})/I_{OH}$  must be less than  $23.4\Omega$  for values of  $V_{OUT}$  between  $V_{DDQ}$  and  $V_{DDQ} - 280mV$ . Impedance measurement condition for output sink DC current:  $V_{DDQ} = 1.7V$ ;  $V_{OUT} = 280mV$ ;  $V_{OUT}/I_{OL}$  must be less than  $23.4\Omega$  for values of  $V_{OUT}$  between 0V and 280mV.

3. Mismatch is absolute value between pull-up and pull-down; both are measured at same temperature and voltage.

4. Slew rate measured from  $V_{IL}(AC)$  to  $V_{IH}(AC)$ .

5. The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC.

**Clock Jitter [ DDR2- 1333, 1066, 800]**

Input clock jitter spec parameter. These parameters and the ones in the table below are referred to as 'input clock jitter spec parameters' and these parameters apply to DDR2-1066 and DDR2-800 only. The jitter specified is a random jitter meeting a Gaussian distribution.

| Parameter                                                    | Symbol               | -1.5 / 1.6 |      | -1.8 |      | -2.5 |      | Unit | Note |

|--------------------------------------------------------------|----------------------|------------|------|------|------|------|------|------|------|

|                                                              |                      | Min.       | Max. | Min. | Max. | Min. | Max. |      |      |

| Clock period jitter                                          | $t_{JIT}$ (per)      | -50        | 50   | -90  | 90   | -100 | 100  | ps   | 5    |

| Clock period jitter during DLL locking period                | $t_{JIT}$ (per,lck)  | -40        | 40   | -80  | 80   | -80  | 80   | ps   | 5    |

| Cycle to cycle period jitter                                 | $t_{JIT}$ (cc)       | -130       | 130  | -180 | 180  | -200 | 200  | ps   | 6    |

| Cycle to cycle clock period jitter During DLL locking period | $t_{JIT}$ (cc, lck)  | -120       | 120  | -160 | 160  | -160 | 160  | ps   | 6    |

| Cumulative error across 2 cycles                             | $t_{ERR}$ (2per)     | -100       | 100  | -132 | 132  | -150 | 150  | ps   | 7    |

| Cumulative error across 3 cycles                             | $t_{ERR}$ (3per)     | -100       | 100  | -157 | 157  | -175 | 175  | ps   | 7    |

| Cumulative error across 4 cycles                             | $t_{ERR}$ (4per)     | -100       | 100  | -175 | 175  | -200 | 200  | ps   | 7    |